如题,和移位寄存器原理差不多,只能校验8位,功能比较单一。

vhdl源程序如下:

- module crc8( /*x^8+x^5+x^4+1*/

- input rst, /*async reset,active low*/

- input clk, /*clock input*/

- input [7:0] data_in, /*parallel data input pins */

- output reg[7:0] crc

- );

- integer i;

- reg feedback;

- reg [7:0] crc_tmp;

- /*

- * sequential process

- */

- always @(posedge clk or negedge rst)

- begin

- if(!rst)

- crc <= 8'b0; /*触发器中的初始值 */

- else

- crc <= crc_tmp;

- end

- /*

- * combination process

- */

- always@( data_in)

- begin

- crc_tmp = data_in;

- for(i=7; i>=0; i=i-1)

- begin

- feedback = crc_tmp[7];

- crc_tmp[7] = crc_tmp[6];

- crc_tmp[6] = crc_tmp[5];

- crc_tmp[5] = crc_tmp[4] ^ feedback;

- crc_tmp[4] = crc_tmp[3] ^ feedback;

- crc_tmp[3] = crc_tmp[2];

- crc_tmp[2] = crc_tmp[1];

- crc_tmp[1] = crc_tmp[0];

- crc_tmp[0] = feedback;

- end

- end

- endmodule

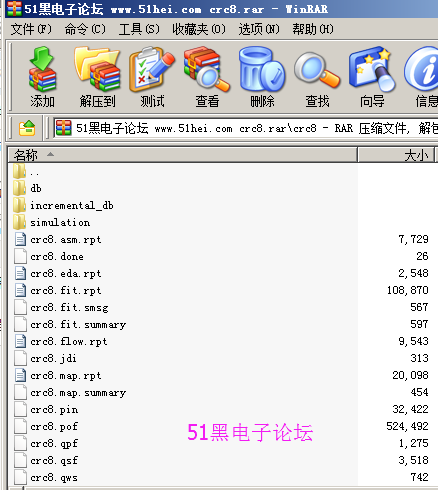

所有资料51hei提供下载:

crc8.rar

(2.27 MB, 下载次数: 15)

crc8.rar

(2.27 MB, 下载次数: 15)

|