fpga播放一首歌

1 实验目的

(1)理解并掌握脉宽调制(PWM )技术的控制方法及基本工作原理。

(2)学习并掌握脉宽调制(PWM )驱动蜂鸣器的实现方法。

2 实验原理

2.1 基本概念

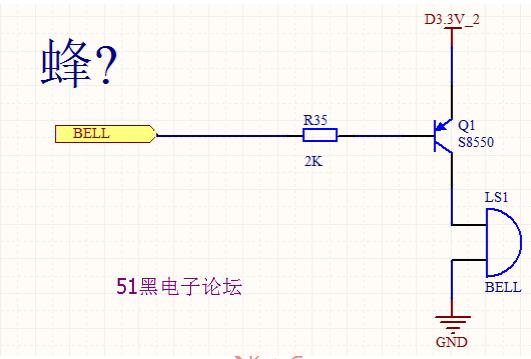

脉冲宽度调制(PWM)是一种对模拟信号电平进行数字编码的方法。通过高分辨率计数器的使用,方波的占空比被调制用来对一个具体模拟信号的电平进行编码。PWM 信号仍然是数字的,因为在给定的任何时刻,满幅值的直流供电要么完全有(ON),要么完全无(OFF)。电压或电流源是以一种通(ON)或断(OFF)的重复脉冲序列被加到模拟负载上去的。通的时候即是直流供电被加到负载上的时候,断的时候即是供电被断开的时候。只要带宽足够,任何模拟值都可以使用PWM进行编码。 有源蜂鸣器和无源蜂鸣器的差别: 这里的“源”不是指电源。而是指震荡源。也就是说,有源蜂鸣器内部带震荡源,所以只要一通电就会叫。而无源内部不带震荡源,所以如果用直流信号无法令其鸣叫。必须用 2K~5K 的方波去驱动它。 有源蜂鸣器往往比无源的贵,就是因为里面多个震荡电路。 无源蜂鸣器的优点是:1。便宜,2。声音频率可控,可以做出“多来米发索拉西(1234567)”的效果。3。在一些特例中,可以和 LED 复用一个控制口 有源蜂鸣器的优点是:程序控制方便 。

开发板上的蜂鸣器是有源蜂鸣器。FPGA 输出低电平,即可让蜂鸣

器鸣响。

Quartus 工程 qsf 文件管脚约束命令,把以下命令拷贝到新建 quartus

工程的 qsf 文件即可完成管脚约束(注意信号名必须相同) :

set_location_assignment PIN_23 -to i_50m_clk

set_location_assignment PIN_28 -to i_rst_n

set_location_assignment PIN_187 -to o_pwm

3 实验步骤

3.1 综合

(1)运行综合工具。

(2)打开项目工程,项目工程存放于以软件开发工具命名的文件夹

中。

(3)编译运行或直接点击下载,下载 FPGA 软件到目标板。

(4)查看软件运行效果

3.2 仿真

请参考视频讲解。

主要命令:

切换仿真路径 cd { 仿真库路径 } ,如: cd

{F:\Verilog_demo\M01_buzzer_pwm\sim};

run 100us:仿真运行时间长度 100us ;

do wave.do:运行波形文件;

vlog ../src/*.v:编译 scr路径下的所有 v文件

vsim:开始仿真命令

quit –sim:退出仿真

4 实验结果

4.1 结果演示

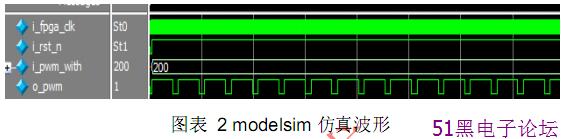

4.1.1 MODELSIM 仿真演示

4.1.2 M ATLAB 数据分析

略。

4.1.3 开发板演示

略。

4.2 特别说明

PWM 的一个优点是从处理器到被控系统信号都是数字形式的,无需进行数模转换。让信号保持为数字形式可将噪声影响降到最小。噪声只有在强到足以将逻辑1改变为逻辑0或将逻辑0改变为逻辑1时,也才能对数字信号产生影响。

对噪声抵抗能力的增强是PWM相对于模拟控制的另外一个优点,而且这也是在某些时候将 PWM 用于通信的主要原因。从模拟信号转向PWM 可以极大地延长通信距离。在接收端,通过适当的 RC 或LC网络可以滤除调制高频方波并将信号还原为模拟形式。

PWM既经济、节约空间、抗噪性能强,是一种值得广大工程师在许多设计应用中使用的有效技术。

源程序如下:

- //==========================================================================

- //Filename :PWM_gen.v

- //modulename:PWM_gen

- //Author :a fei

- //Date :2012-5-16

- //Function :PWM产生器,输出的pwm驱动蜂鸣器

- //Uesedfor :

- //Taobao :

- //E-mail :2352517093@qq.com

- //==========================================================================

- module PWM_gen(

-

- i_fpga_clk ,

- i_rst_n ,

-

- i_pwm_with ,

-

- o_pwm

-

- );

- input i_fpga_clk ;//50MHz

- input i_rst_n ;

-

- input [19:0] i_pwm_with ;//改变数值可控制PWM的高电平宽度

- output reg o_pwm ;

-

-

- //=======================================

- //分频计数器

- //=======================================

- reg[19:0] pwm_cnt ;

- always @ (posedge i_fpga_clk or negedge i_rst_n)//时钟沿加1

- if(!i_rst_n)

- pwm_cnt <= 20'b0 ;

- else if( pwm_cnt==20'hfffff)

- pwm_cnt <= 20'b0 ;

- else

- pwm_cnt <= pwm_cnt+1'b1 ;

-

- always @ (posedge i_fpga_clk or negedge i_rst_n)

- if(!i_rst_n)

- o_pwm <= 1'b0 ;

- else if(pwm_cnt<=i_pwm_with)

- o_pwm <= 1'b1 ;

- else

- o_pwm <= 1'b0 ;

-

-

- endmodule

所有资料51hei提供下载(包含完整的设计报告):

M01_buzzer_pwm.zip

(2.38 MB, 下载次数: 97)

M01_buzzer_pwm.zip

(2.38 MB, 下载次数: 97)

|