FPGA dds的全套设计资料分享给51hei的朋友们,有需要可以下载学习。

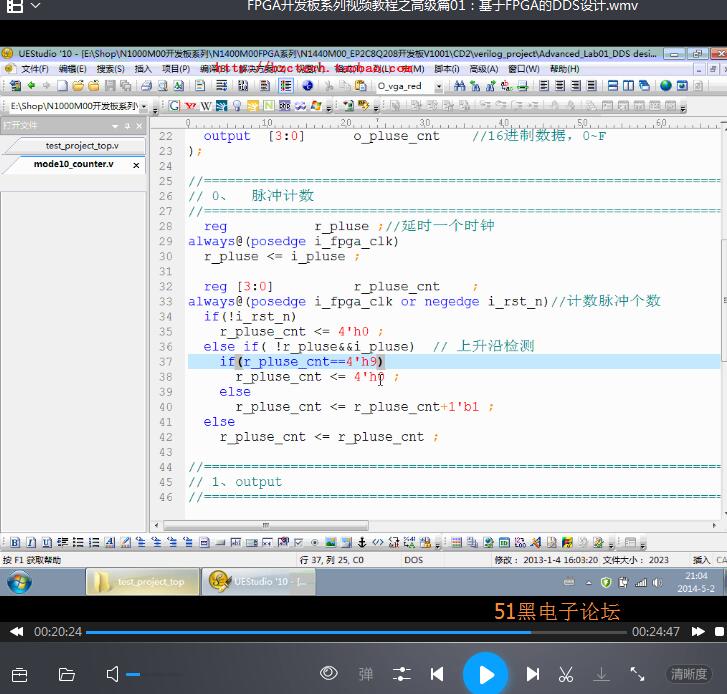

下面是DDS频率合成器视频教程内容截图(代码讲解):

部分源程序如下:

- `timescale 1ns / 1ps

- /*==============================================================================

- Engineer : Xjtao

- Module Hierarchy : top function module

- Design Name : dds_module.v

- Module Name : dds_module

- Project Name : test_project_top.qsf

- Target Devices : Altera

- Tool versions : QUARTUSII11.0/Windows XP

- Description : DDS模块实现将cos及sin数据产生,输出频率:(Fs*i_nco/500)MHz

- Dependencies :

- Revision : 0.01 - File Created

- Additional Comments : ROM存储数据的个数,fs/fmin=25/0.05=500

- ==============================================================================*/

- module dds_module(

- input i_fpga_clk ,//25MHz

- input i_rst_n ,

- input [8:0] i_nco ,//频率控制字

- output [7:0] o_cos ,//余弦波

- output [7:0] o_sin //正弦波

- );

- //================================================================================

- // 0、 频率控制字累加,相位累加

- //================================================================================

- wire [8:0] w_rom_addr ;

- dds_phase_acc #(

- .NCO_WIDTH (9 ), //nco配置位宽

- .ADDR_WIDTH (9 ) //输出地址位宽

- )u0_dds_phase_acc (

- .i_fpga_clk (i_fpga_clk ) ,

- .i_rst_n (i_rst_n ) ,

- .i_frq_nco (i_nco ) ,

- .o_rom_addr (w_rom_addr )

- );

-

- //================================================================================

- // 1、 根据累加相位查找cos及sin的ROM,产生正余弦信号

- //================================================================================

- wire [7:0] w_cos ;

- wire [7:0] w_sin ;

- dds_cos_rom u1_dds_cos_rom(

- .i_fpga_clk (i_fpga_clk) ,

- .i_rst_n (i_rst_n ) ,

- .i_rd_addr (w_rom_addr) ,

- .o_cos (w_cos )

- );

- dds_sin_rom u2_dds_sin_rom(

- .i_fpga_clk (i_fpga_clk) ,

- .i_rst_n (i_rst_n ) ,

- .i_rd_addr (w_rom_addr) ,

- .o_sin (w_sin )

- );

-

- //================================================================================

- // 2、 output

- //================================================================================

- assign o_cos = w_cos ;

- assign o_sin = w_sin ;

-

- //================================================================================

- endmodule

所有资料51hei提供下载:

Advanced_Lab01_DDS design.rar

(13.78 MB, 下载次数: 72)

Advanced_Lab01_DDS design.rar

(13.78 MB, 下载次数: 72)

|