这个是一个基于CD4046锁相环的频率合成器实验,其中重点描写了调试过程,计分模块调试和联合调试及调试过程中遇到的问题及解决方法。

课程设计报告

题 目: 频率合成器

课程名称: 大规模IC应用技术

学 院: 工学院

设计题目

基于cd4046锁相环的频率合成器

学生姓名

所在学院

专业、年级、班

设计要求:

(1)设计制作一个频率步进100hz的频率合成器;

(2)频率抖动不超过100hz;

(3)频率范围在300-400k。

学生应完成的任务:

(1)理解频率合成器设计任务,并查阅相关文献资料;

(2)确定任务设计方案,进行方案论证、比较,确定总体设计方案;

(3)开始设计模块电路,并计算参数,以及选择适当的元器件;

(4)根据确定的方案进行PCB制板、安装、焊接、调试,验证各项技术指标;

(5)按课程设计指导书的要求,编写课程设计报告书。

参考文献:

1.《模拟电子技术基础》,童诗白,高等教育出版社.

2.《电子线路设计与应用》,臧春华,高等教育出版社.

3.《电子线路》(第四版),谢嘉奎,高等教育出版社.

4.《CMOS集成电路应用设计》,罗国新,福建科技出版社.

工作计划:

收集文献资料 理解设计任务,查阅相关文献 一天

确定设计方案 方案论证、比较,确定总体设计方案 二天

单元电路设计 设计模块电路,计算参数,器件选择 三天

组装调试 根据确定的方案安装调试,验证各项技术指标 二天

课程设计说明书 按课程设计指导书的要求,编写设计报告书 二天

基于cd4046锁相环的频率合成器设计

摘 要:CD406锁相环频率合成器以CD4046芯片为核心,加以外围电路搭建而成的一个以一个频率为标准,可以输出多个频率,并且十分的准确稳定,适用于很多领域。

本次实验的频率合成器是最基础的应用,没有非常好的性能,只是一个刚入门的新手的试验电路,并不能运用于日常生活。同时准确度与稳定性也相对较低。

目 录

1. 设计背景

1.1设计的目的

1.2设计的要求

2. 设计方案

2.1设计原理图

2.2设计PCB

3. 方案实施

3.1 PCB的制作

3.3元器件焊接

3.3 电路板调试

4. 结果与结论

4.1 实验结果

4.2 实验结论

5. 收获与致谢

6. 参考文献

1. 设计背景1.1设计的目的- 可以熟练运用锁相环模块

- 理解锁相环各个参数的作用

- 学会根据不同的情况去调整锁相环不同的参数

1.2设计的要求1、设计制作一个频率步进100hz的频率合成器; 2、频率抖动不超过100hz; 3、频率范围在300-400k。 2. 设计方案

2.1设计原理图

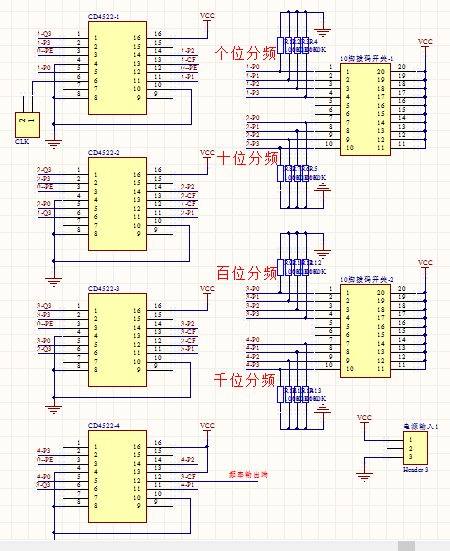

先由晶振产生一个8MHz的信号,经过80000分频变为100Hz的信号;然后输入CD4046的14脚(相位比较器2),VCO的输出信号经过N分频后变为需要得到的信号频率再输入到4046的3脚与100Hz的信号进行对比,最后两个信号频差位0时即可得到我们需要的信号。 2.1.1晶振原理图

以8M晶振为核心搭建的一个能输出8MHz信号的模块。 2.1.2 M分频

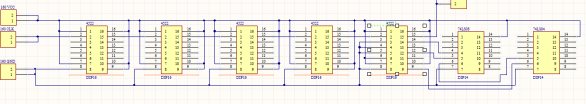

M分频模块是以5个4522芯片为核心,辅以74ls08和74ls04搭建的一个80000分频模块。对晶振的8MHz信号进行分频变为100Hz信号。 2.1.3锁相环

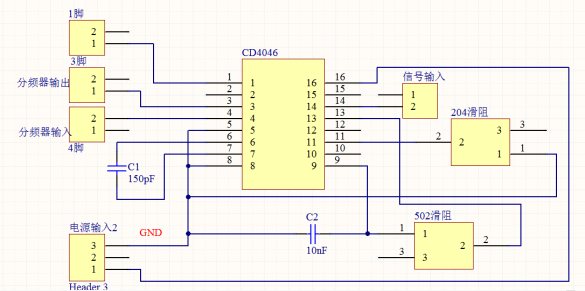

该模块是在上一个实验的基础上加以更改后得到的。因为实验要求是300k~400k的带宽,电压为10V,但我们做出来的电路板必然会存在误差,所以吸收以前的教训,我们将带宽变宽,变为200k~500k,这样上下都有100k的误差范围就可以在一定范围内抵消读数、焊接、制板和环境带来的误差,从而更好的达到实验要求。

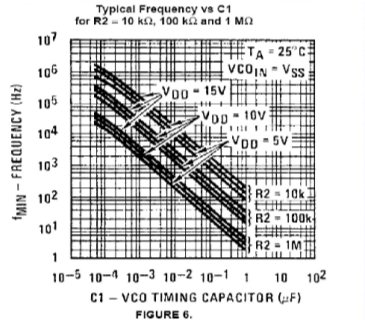

图一

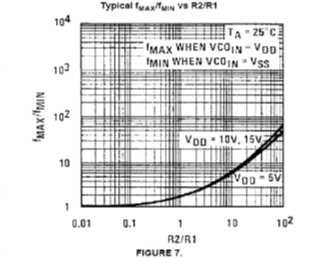

图二 我们已知R2=10k,fmin=200k,fmax=500k,Vcc=10V,由图一可知,C1大约在15pF左右。fmax/fmin=2.5,所以R2/R1=2,所以R1=5K。R3与C2的值可以通过公式计算得出,2fc=2fl=300k,所以τ=1/300000π=0.00000106。此时取 R3=1k,C2可以用1nF。为了以防万一我在R1和R3后面又接了滑阻,方便更改。 2.1.4N 分频

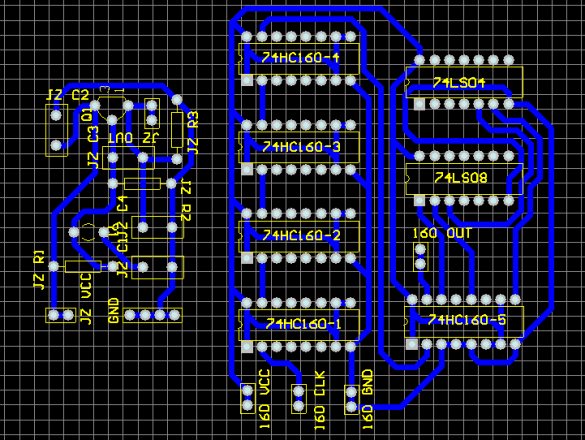

在4522的基础上加上拨码开关,通过拨码开关控制分频大小。 2.2设计PCB晶振及M分频PCB图

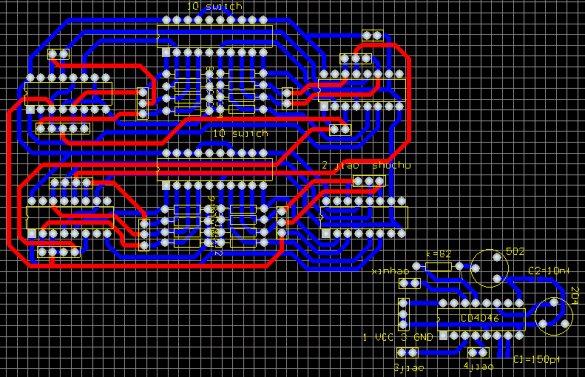

锁相环及N分频PCB图

其中红线部分为顶层线路,蓝色部分为底层线路,又因为是单层板,所以红线部分预留出排针焊盘然后通过飞线连接。 3. 方案实施3.1 PCB的制作- 将图打印到油印纸上

- 将图裁下来与板贴在一起放进热转印仪上,来回4-5遍

- 将油印纸撕下,看线路是否完整,将板放入腐蚀液中腐蚀

- 腐蚀完将碳磨掉,将板清洗干净

- 对应焊盘打孔

3.3元器件焊接对应原理图与PCB图,将原件一个个焊接上,最好是按顺序焊接,这样可以检查一遍电路;也可以按原件的大小焊接,先焊接小原件,最后焊接大原件,这样会方便很多。

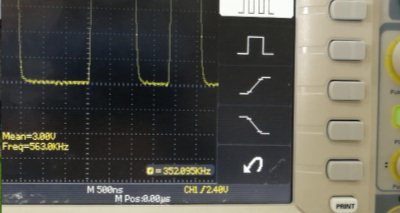

3.3 电路板调试3.3.1分模块调试1、晶振调试 接入5V电源,接地,输出接示波器,观察到8MHz的波形,该模块度欧式确定的,只要不是焊接出错,一般都不会出问题 接入5V电源,从函发上接入8MHz,Vpp=10V的信号,输出接示波器,观察到100.2Hz的信号。这里会有一点误差,但想不出办法消除,因为0.2Hz的误差有很大可能是焊接及环境影响等不可调因素影响的,很难改变。 接入10V电源,将3,4脚接一起,函发接输入,输出接示波器,先将函发设置为1kHz,Vpp=10V,示波器显示为221.2kHz,将函发的频率以5k的频率步进,测试一下锁相环的锁定范围是否能达到400kHz,最后锁相环失锁在485.3kHz,锁相环锁定范围在221.2kHz~485.3kHz,包括了300k~400kHz,所以达成目标。 将频率分别调为301.3kHz,349.8kHz,399.5kHz,锁相环都可以锁住。 接入5V电源,函发接输入端,输出端接示波器。,函发设置为100kHz,拨动拨码开关,将个十百千位都拨几遍,观察到分频出正确的频率。 3.3.2合成调试现将晶振模块接电源,输出接示波器,观察到8MHz的波形;将晶振输出接入M分频,M分频接入5V电源,输出接示波器,观察到100.3Hz的频率,有0.3Hz的误差存在。到这里可以确定晶振加M分频基本没问题,接下来测锁相环加N分频模块。先单侧锁相环模块,再次确定锁相环模块是没问题的,将锁相环模块与N分频模块接在一起,接上电源,给锁相环供电10V,N分频供电5V,锁相环输入接函发,N分频输出接示波器,函发设置为100Hz,Vpp=10V,调整拨码开关,将千位拨为1100即3000分频。示波器显示也为300.01k,在将百位拨为1010即500分频,加上前面的3000分频,即3500分频,示波器显示为350.03k,存在0.03k的误差,在允许范围内。最后将M分频的输出接锁相环的输入,开始总的测试。现将拨码开关千位拨为1100,十位拨为1000,个位拨为1100,即301.3k,但示波器显示为混乱的波形,这有可能是M分频与锁相环直接的问题,那么最大的可能就是锁相环读取不到信号,因为,只要能读取到信号,那么示波器最起码有一个稳定的波形,而不是混乱的波形,那么就需要给M分频的输出抬高电压,这在做抬压电路的话太麻烦,所以最直接的办法就是给M分频供电提高,这会有将芯片烧坏的风险,但芯片还有剩余,可以试试,然后我就供电提高到6V,还是不行,再提高到7V,这时示波器出现了波形,但频率差了1K多,超出了误差范围。不行,但我觉得这是之前M分频中那多余的0.3Hz造成的,要去除很难。后来想了一个取巧的办法,就是在拨码开关上下降1k的频率来拉低最后的输出,结果是可以的。 4. 结果与结论4.1 实验结果

4.2 实验结论实验要求捕获到301.4kHz,351.9kHz,399.8kHz,实测得到301.4kHz,352.0kHz,399.9kHz,虽然有一点误差,但在允许的范围内。 误差分析: - 焊接工艺太差

- 飞线自身的电阻印象

- 电源不稳定,一直跳动

- 环境温度影响

5. 收获与致谢通过这次实验,学会了多种模块合并电路的调试过程及对不同错误的应对方法,也更加深入的了解了锁相环的引用,以及在设计电路方面的小技巧。很庆幸可以有这样的一次期末考试,和这么困难的一次实验挑战。谢谢老师给予的这次机会。

完整的Word格式文档51黑下载地址:

基于CD4046锁相环的频率合成计.doc

(3.55 MB, 下载次数: 47)

基于CD4046锁相环的频率合成计.doc

(3.55 MB, 下载次数: 47)

|