FPGA电子琴 大家共享一下

目录

第一章 绪论 3

1.1 EDA简介 3

1.2芯片介绍 4

1.3 Cyclone(飓风)系列介绍 4

第二章 模块介绍 6

2.1设计分析 6

2.2硬件电子琴分析 6

2.3 乐曲自动演奏机分析 6

2.4整体设计分析 6

2.5 设计流程 7

第三章 功能划分与模块划分 8

3.1自动演奏模块 8

3.2 自动演奏设计方案 8

3.3硬件电子琴模块 8

3.3.1硬件电子琴设计方案 9

3.3.2设计步骤 9

第四章 课程设计原理 10

4.1硬件电子琴设计原理 10

4.2乐曲自动演奏设计原理 10

4.3各模块的实现方法 11

4.3.1选择器模块实现方法 11

4.3.2自动演奏模块实现方法 11

4.3.3硬件电子琴模块实现方法 12

第五章 实验箱设计 13

5.1硬件电子琴模块程序 13

5.2乐曲自动演奏机程序 14

5.3 选择模块程序 18

5.4顶层文件程序 18

第六章 实验图形文件 20

6.1管脚锁定图 20

6.2DXP原理图及封装 21

6.3任务完成情况说明 22

6.4硬件连接图 22

总结 25

参考文献 26

附录:项目实物图 27

3.3.1硬件电子琴设计方案

(1)根据硬件电子琴演奏的基本原理设计出适合EDA多功能试验箱的源程序,通过分频模块得到12MHZ的晶振;源程序编写完成,编译调试后,在实验箱上验证其功能;

(2)验证模块是否能完成实践要求的所有功能;然后去掉分频模块,将功能模块做适当的修改后,编译调试成功后,将其下载到CPLD实验板上。

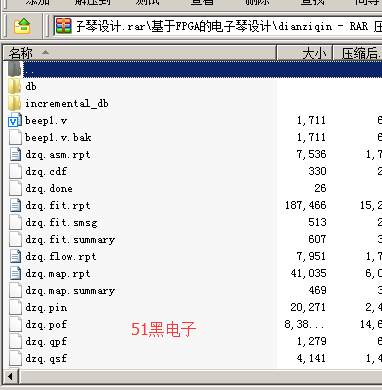

3.3.2设计步骤

(1)在Quarters II中建立一个工程项目文件beep1.qpf。并在该项目下新建Verilog HDL源程序文件beep1.v,输入程序代码并保存,进行综合编译,若在编译中发现错误,则找出并更正错误,直至编译成功为止。

(2)选择目标器件并进行引脚锁定。将未使用的管脚设置为三态输入。

(3)对该工程文件进行全程编译处理。若在编译过程中发现错误,则找出并更正错误,直到编译成功为止。

(4)将产生的beep1.sof输出对FPGA进行配置。按下按键KEY1~KEY8就可以开始使用电子琴来演奏音乐了。

全部资料51hei下载地址:

基于FPGA的电子琴设计.rar

(5.14 MB, 下载次数: 152)

基于FPGA的电子琴设计.rar

(5.14 MB, 下载次数: 152)

|