自己上课时候写的小作业,主要用FPGA和VHDL实现了一小闹钟,由于我的Altera的开发板资源有限

数码管用了4个,点阵用了一个。

主要功能:1.能正常跑表,设置跑表时间

2.闹铃声音可以由高到底,三种频率(你可以在我的基础上加)

3.懒人起床模式

4.多人使用模式

还有些小功能在我的论文里,有兴趣的可以看看(请用Quartus 12.0以上版本打开,不然备注没法看)

不足之处:if用的太多导致逻辑单元爆炸了,你们 需要优化的的话,多用case代替if

基于FPGA的智能闹钟的设计与实现

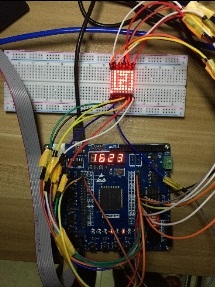

序言: 本FPGA的智能闹钟的是基于Altera Cyclone IV EP系列芯片开发设计的。由于实验平台的限制,外设设备选择了一个4管数码管,蜂鸣器,独立按键4个,拨码开关4个和8X8的Led点阵一个。

1.带有设置功能的时钟表(设置时间用Led点阵显示字母S来表示)。 2.带有设置功能的闹铃(设置时间用Led点阵显示数字1或2来表示)。 3.多人使用模式(这里设置了用户1,用户2,使用状态用Led点阵来显示)。 4.自然醒的铃音(在闹铃响的时候,使用蜂鸣器的声音逐渐变大的模式,符合人体规律,任意独立按键可以关闭闹铃)。 5.懒人起床模式(通过拨码开关设置,开启时,会在60秒内,响3次,每次10秒。两次之间间隔10秒,可以通过任意的独立按键关闭本次响铃,但是,下次仍会响,直到3次结束)。  设计方案 设计方案

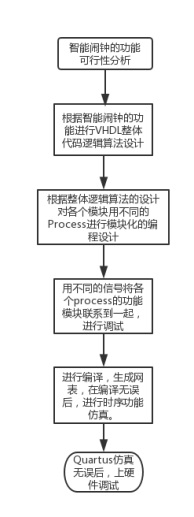

整体设计的流程图如下

本系统使用的50MHz的晶振,故此,用一个Process进行分频,1Hz用于正常的时间记时间。此外生成一个1000Hz用于时钟时间在数码管上显示时选管。(运用动态扫描的方式来驱动数码管)。而使用者,只需要通过把拨码开关1拨到ON且拨码开关2在OFF的时候,才能对时钟的时间进行设置。 闹铃模式的基本实现逻辑是:使用一个IF语句,当设置的秒,分的所有值与正常时钟跑表时间一致的时候让逻辑标志值为真,驱动闹铃的process。使用者,只需要把拨码开关2拨到OFF,其余的随意设置,才能对闹铃的时间进行设置。闹铃时,按任意的独立按键可以关闭闹铃。 通过拨码开关3,在ON时表示用户1在使用闹钟,在OFF时表示用户2在使用闹钟。 通过使用分频器分出3种不同的频率,设置3种频率驱动蜂鸣器的总时间为10秒,每种频率分别占用3.333秒左右。 通过拨码开关4,拨码开关拨到ON的时候,开启懒人模式,彻底的关闭懒人模式只有将拨码开关拨到OFF或等3次闹铃结束的时候。如果在闹铃的期间,随意的按一下独立按键开关会终止本次闹铃,但是下次闹铃仍会继续。

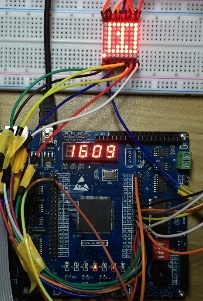

用户1在正常使用时的硬件效果图 用户1在正常使用时的硬件效果图

图1 表示用户1设置闹铃中 图2 表示用户1正常使用中

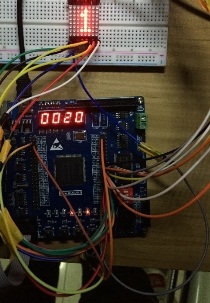

图3 表示用户2正常使用中 图4 表示用户2设置闹铃中 图3 表示用户2正常使用中 图4 表示用户2设置闹铃中

图5 表示用户1或者2再设置时钟时间中

图6 表现用户2闹铃中

通过这次FPGA的课程设计,我对FPGA的整体认识上了一个新的台阶,以前的实验课只是从事单个的逻辑功能芯片的实现,而此次基于FPGA的智能闹钟的设计与实现写了足足600行的代码,大大的提高了我的编程和逻辑分析能力。也初步具备分析和设计一个较为复杂的项目的能力。此外,在这次课程设计中我也认识到我的不足之处,首先,在编程风格上的缺陷,自己对FPGA的寄存器和逻辑单元这两个最重要的资源理解不到位,导致自己在编程的过程中没有节约这两项资源。例如,过多的使用IF-ELSE语句而不用CASE语句导致产生大量的优先级的编码器从而使得只写了600行代码后发现逻辑单元不够用了。其次,本次设计中,时序和逻辑比较复杂,后期的自学中才发现,应对复杂的逻辑设计,VHDL中的有限状态机(Finite State Machine)能很好的应对,远比不断地使用逻辑标志方便和高效。可以说,这次课程设计收益颇多,需要进一步的学习和总结。才能早日在FPGA的设计与开发中取得一定的成绩。

全部资料51hei下载地址: |