|

高速先生成员--黄刚 现在稍有经验的layout工程师都知道在BGA里面不同封装的去耦电容从小到大应该按下图这样放置:放置的顺序是从小电容到大电容采取从近到远的方式。

稍微具有SI,PI知识的工程师会说这样有利于改善电源PDN系统的性能,理论上是电容都应该离芯片引脚越近放置越好,尤其是小电容,比大电容更应该靠近芯片端。为什么呢?专业用语叫小电容的去耦半径更小。所谓去耦半径,无非是研究噪声源和电容补偿电流之间的相位关系。当芯片电流发生变化时,会在电源平面的一个局部区域内产生电压波动,由于信号在介质中传播需要一定的时间,因此从局部电压波动到电容感知到这一波动之间有一个时间延迟。同样,电容的补偿电流到达波动区域也需要一个延迟,因此必然造成噪声源和电容补偿电流之间的相位上的不一致。在严谨的场合中,Chris就是会这样来描述这个名词!

说完上面这一段,相信有不少粉丝感觉Chris什么都没说似的。行吧,下面就以Chris的理解给大家解释(fan yi)一下。从应用来说,就是每个电容在与它的自谐振频率f(波长为λ)相同频率下的噪声补偿效果最好,相位差越小越好,λ/4时电容失效,出现反谐振。在实际应用中,我们一般取小于λ/50比较稳妥。

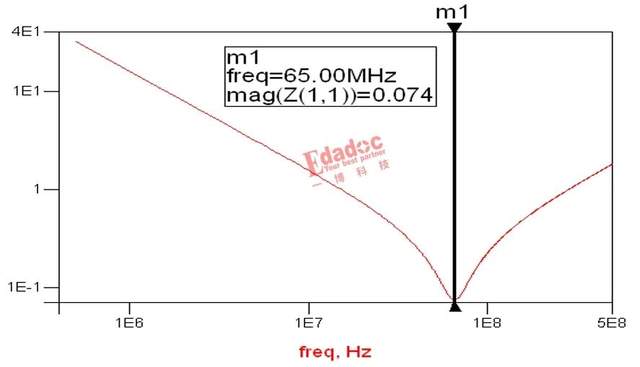

例如下面这个0402封装的10nf的一款电容,它的真实阻抗如下所示:

从它自身的Z阻抗曲线来看,谐振频率在65MHz,也就是我们通俗说的这个电容的去耦频段在65MHz以内。

然而实际情况是电容到达Pin或多或少都会有一定的距离,这里假设距离为50ps(大概300mil左右),如下:

这样的话,这两者的z阻抗曲线对比就有差别了,经过传输线之后的z阻抗谐振点提前,在原谐振点的位置阻抗增加到了0.813欧姆。谐振点频率也会相应的往前提了,就相当于这个电容的去耦频段就不能达到那么高频段了。Chris稍微计算一下去耦半径:谐振频率为65MHz,波长为92.7inch(假设在fr4中传输),那么λ/50=1.85inch(约300ps),然而从结果上看到50ps的时候变化都已经比较明显了。

当然上面说的还是理论,只是对比于文字来说有点数字显得没那么理论。那应用到具体的PCB设计项目中会是怎么样的呢?行!Chris大概做了一个简单的仿真case,如下所示:1个用于仿真的4层板,一个小的BGA和一个0402-100nF的小电容都放在top层。 其中中间L3层是电源层,通过仿真看看电容放在距离BGA不同距离情况下PDN阻抗曲线的变化。

首先看到我们用的这个0402-100nF电容本身的PDN阻抗曲线如下所示:所以看到这个电容本身的谐振频段在25MHz。这是一个初始的基准,也就是不放在PCB上的情况下,这个电容自己的特性展示。

那么我们把电容放在距离BGA最近的位置上,距离BGA大概3mm的样子。

在这个case下,BGA芯片的PDN阻抗曲线(蓝)和单纯电容的PDN阻抗曲线(绿)相比,就有了明显的恶化,去耦的频段大概变差了7MHz,这个是非常大的恶化了。

当然,单纯理想的电容和放到PCB板上两者肯定会变差不少。为了让大家更好的感觉下摆放距离和PDN阻抗曲线的恶化程度,我们分别在距离BGA从上面的3mm,再拉大5mm和10mm的距离,如下所示:

从仿真结果来看,放远5mm(橘)和原来放在3mm的距离(蓝)的PDN阻抗曲线对比,去耦频段减少了2MHz。再放远5mm(红)和放远5mm(橘)又减少了1.4MHz的样子。电容本身可以去到25MHz多的去耦频段,随着距离越来越远,有效频段直接快打了个骨折!

当然这个只是一个很简单的仿真case,BGA很小,叠层也只有4层,电容也才1个。Chris只是大概通过这个仿真case让大家形象的看到具体项目中电容随着位置放远之后的恶化。不同项目的分析方法其实也是一样,只不过电容和层数更多,BGA或者PCB板更大,万变不离其宗。一名优秀的工程师不仅要知道理论,更要知道理论怎么用于实际,从而来解决实际的问题哈!

|