本帖最后由 电子爱好者没错 于 2023-8-22 20:07 编辑

FPGA 开发专题 | 初识 FPGA 开发流程和仿真工具

目录:

- 一、FPGA 开发流程

- 二、FPGA 仿真工具

- 三、开设 FPGA 专题咯D:\Xzhao\Documents\OfficialAccounts\Article\2023.07.01\photos\Apolong_at_Shougang_Jiaohuachang_(20230322140939).jpg

图:北京首钢园内的无人驾驶小巴士

全文 2031 字,阅读大约需要 4 分钟

第一台真正意义上的自动驾驶汽车最早可追溯至 1980 年代,随着近年来人工智能和新型传感器(硬件)的快速发展,自动驾驶相关行业迅速进入红海。尽管相关技术已经逐步趋于成熟,但如何更快地识别路况、提高系统判别实时性一直是学术界和工业界追求的目标。 FPGA 作为一种半定制化电路,具有 ASCII 芯片所没有的可编程的灵活性,又具有一般 CPU 所不具备的硬件层并行数据处理的优势,广泛用于图像处理、机器视觉、无人驾驶等领域。在某种程度上,FPGA 可兼顾人工智能的大量计算需求和工业应用中低延时的要求。从前几年神经网络软件算法的爆火到近些年来 “用 FPGA 加速神经网络 ” 逐渐火出圈,让我们看到了技术发展自上而下的革新,从软件到硬件,从高层抽象到底层电路,硬件的天花板作用越发彰显。

本文首发于在下石同学 未经授权 不得转载

文 | 在下石同学

一、FPGA 开发流程 FPGA (Field Programmable Gate Array),即现场可编程逻辑阵列。

现场可编程逻辑门阵列(Field Programmable Gate Array,缩写为FPGA),它以PAL、GAL、CPLD等可编程逻辑器件为技术基础发展而成。作为特殊应用集成电路中的一种半定制电路,它既弥补全定制电路不足,又克服原有可编程逻辑控制器逻辑门数有限的缺点。

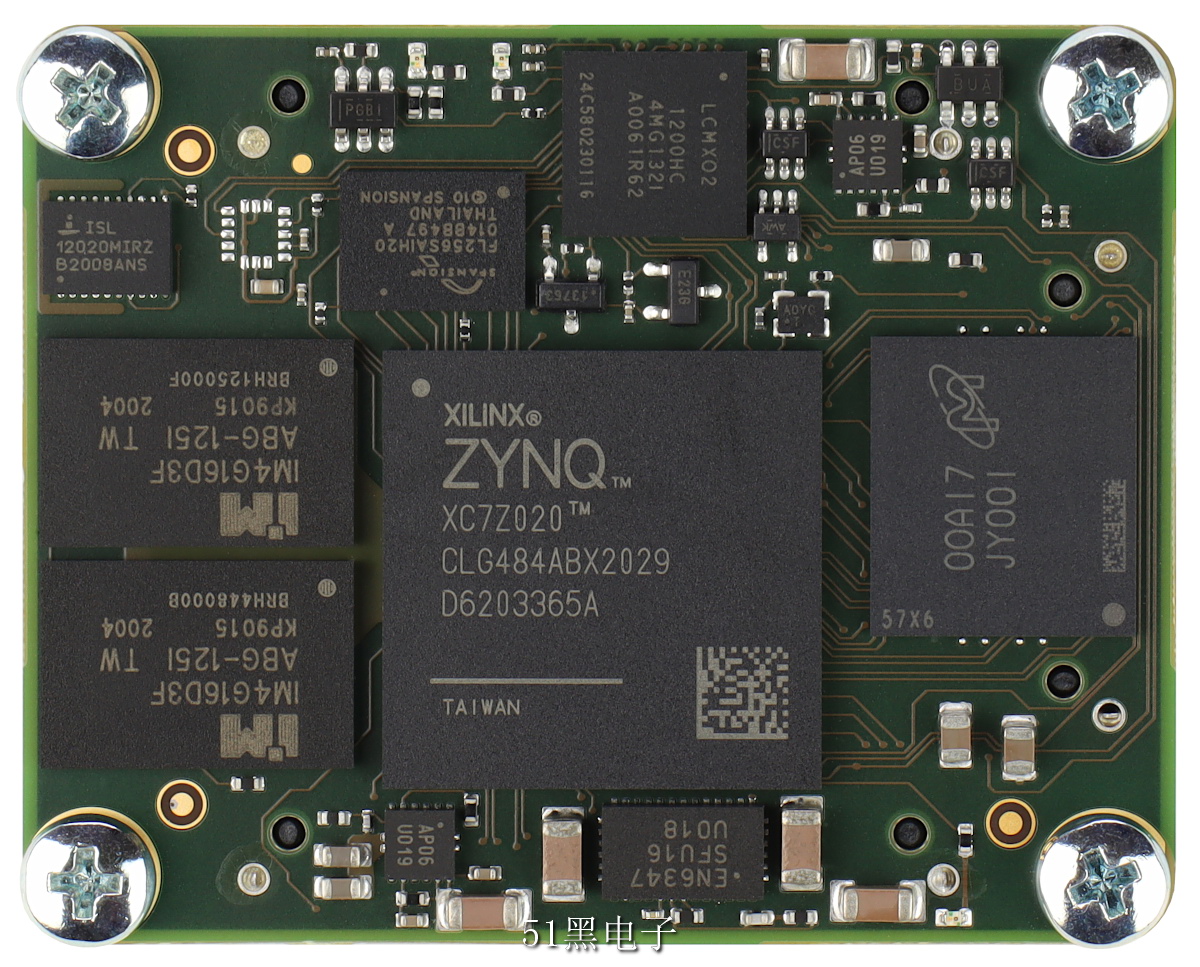

图:ZYNQ-7020 核心板

FPGA 作为一种半定制化电路,具有 ASCII 芯片所没有的可编程的灵活性,又具有一般 CPU 所不具备的硬件层并行数据处理的优势,广泛用于图像处理、机器视觉、无人驾驶等领域。在某种程度上,FPGA 可兼顾人工智能的大量计算需求和工业应用中低延时的要求。从前几年神经网络软件算法的爆火到近些年来 “用 FPGA 加速神经网络 ” 逐渐火出圈,让我们看到了技术发展自上而下的革新,从软件到硬件,从高层抽象到底层电路,硬件的天花板作用越发彰显。

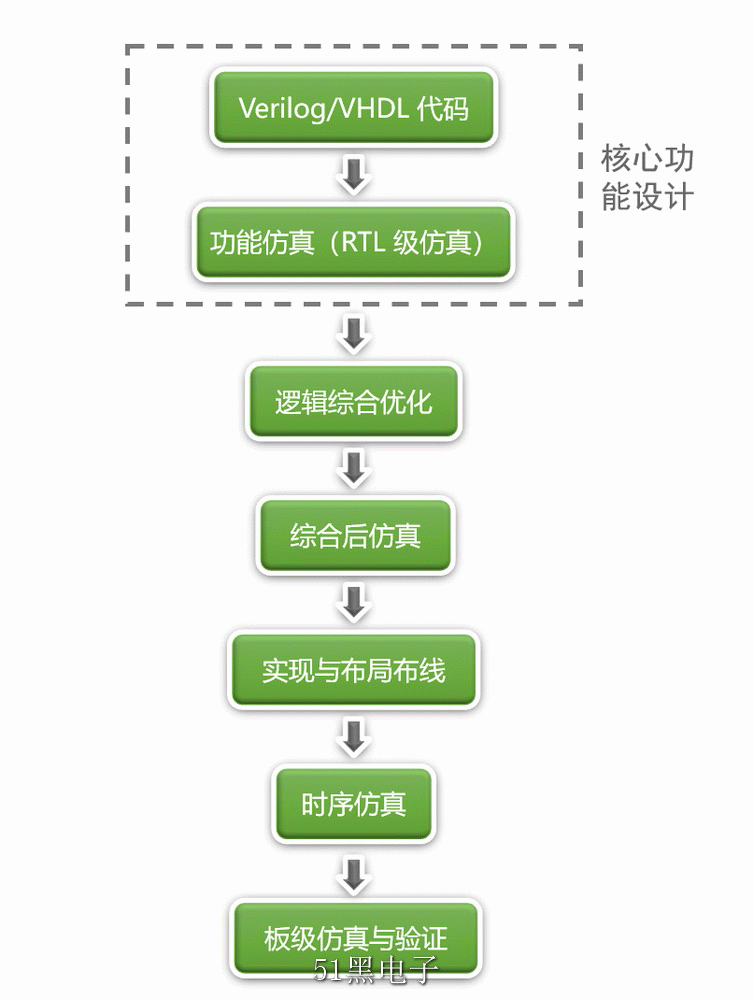

相对于一般编程语言开发,FPGA 的开发过程更为繁琐,尽管 FPGA 也有 Verilog/VHDL 这样的代码语言去描述和定义逻辑功能,但 Verilog/VHDL 是硬件描述语言,跟 C/C++ 不同的是,经过后续的综合以后,可以直接生成对应的电路。 FPGA 的开发流程主要包括 7 个部分,如下图所示:

图:FPGA 开发流程 下面简要聊聊各个部分的作用(敲重点!)

- Verilog/VHDL 代码:我们使用硬件描述语言去编写对应的电路模块,实现逻辑功能,这部分是整个设计中占比最大的一环

- RTL 级仿真:这部分是功能仿真,类似于 C/C++ 开发中的 debug 功能,我们需要对写好的 Verilog/VHDL 代码进行测试和检查,以验证我们的功能模块没有出现逻辑错误,一般会编写 Testbench 代码并编译生成波形文件,通过波形文件就可以判断逻辑功能是否有误

- 逻辑综合优化:综合是将上述过程中较为高级的硬件描述语言转化为更为底层的实现,最终编译成由与/或/非门、RAM、触发器等基本逻辑单元组成的网表,但并不代表真实的门电路

- 综合后仿真:只考虑逻辑和功能的实现是不严谨的,实际上真实门电路的信号传输一定伴随着延时,会导致各种竞争冒险和时序紊乱的现象发生,这部分会把标准的延时参数送入仿真模型中二次核验,更加贴近真实情况

- 实现与布局布线:通过以上过程已经得到了电路的网表,实现和布局布线的过程就是把网表配置到具体的 FPGA 芯片中

- 时序仿真:也称为后仿真,时序仿真把上一步布局布线的延时都考虑进去,并标注到网表中,是芯片延时信息的最真实、最准确的反映

- 板级仿真与验证:一般用于高速信号,对信号完整性等进行综合分析

我们可以看到,FPGA 的开发过程是非常折腾的,通过 RTL 级仿真、综合后仿真、时序仿真三大仿真实现从逻辑到门电路时延的反馈和调整,好在大部分工作都由 EDA 软件工具帮我们完成了,实际上,在大部分开发中,整个流程中最核心的还是前两部分,Verilog/VHDL 代码和RTL 级仿真。

二、FPGA 仿真工具 FPGA 的仿真工具有很多,但由于 FPGA 芯片本身专利问题及制造的差异性,基本上某一具体型号 FPGA 芯片的开发工具和该器件厂商是绑定的,不像 ARM 这种嵌入式通用处理器有更加完善和通用的开发工具链。当然,对于一般 Verilog/VHDL 的 RTL 级层面仿真,不涉及具体的芯片型号,市面上的仿真工具都可以使用,常见的如大牌厂商 Altera(现已被 Intel 收购)家的 Quartus,Xilinx 家的 Vivado,Mentor Graphics 家的 ModelSim,Cadence 家的 NCSim,开源的 Icarus Verilog 以及一些国产方案等。

注:本文用到的所有软件相关参考链接都会附在文末 工具 | 厂商 | 说明 | Quartus | Altera |

| Vivado | Xilinx |

| ModelSim | Mentor Graphics | PE、DE、SE 三个版本,非常流行 | NCSim | Cadence | Incisive 工具套件,用于 ASIC 设计 | Icarus Verilog | GNU GPL | 开源、轻量 | TangDynasty | 上海安陆科技 | 国产厂商 | Pango Design Suite | 紫光同创(深圳) | 国产厂商 | procise | 复旦微(上海) | 国产厂商 |

Altera 和 Xilinx 家的 FPGA 是市场占有率最高的,涵盖了 FPGA 设计的整个流程,ModelSim 是 FPGA 仿真最受欢迎的软件,非常流行, Icarus Verilog 支持 GPL 协议,开源免费且轻量,也是 FPGA 开发中 RTL 级仿真值得使用的软件,搭配 GTKwave,出仿真图非常方便,功能强大。

三、开设 FPGA 专题咯 本文简单介绍了 FPGA 开发的基本流程和常见的仿真工具,太长时间没更新了所以赶紧水一篇。 开设 FPGA 专题咯,就当作 FPGA 专题的开篇吧!

文中涉及 FPGA 软件工具参考网站:

除了在51黑电子论坛发帖,大家也可以关注我的微信公众号:在下石同学

让技术有深度,让科普有温度~ 旨在分享电子电路、嵌入式、编程相关的笔记和教程,包括:电子电路设计、PCB设计、通信协议、嵌入式编程等。还会不定期分享有趣好玩的开源项目 平时学习工作很忙,偶尔鸽一下~ 会坚持更新的!

微信扫码可以关注我的公众号(哈哈纯技术分享,不存在任何打广告行为,放心食用):

|