|

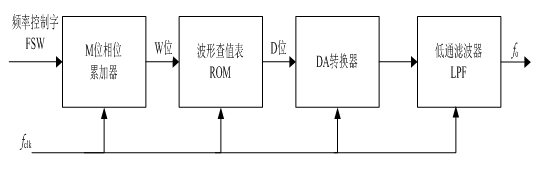

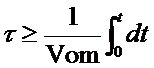

函数信号发生器设计报告 参赛学校:河池学院 参赛作者:梁平 摘要 本系统基于直接数字频率合成(DDS)技术,系统以Luminary Micro公司的Stellaris系列的ARM1138为控制核心平台,配合DAC电路,设计了完成了低频三相函数信号发生器,频率范围100Hz~20KHz,频率稳定度优于10-5-,最小步进1Hz,频率精度优于0.1%。采用NE5532的功放电路使得10kΩ负载上的电压峰-峰值Vopp≥10V。利用DDS原理同时产生FM调制波形及占空比可控、频率可预置、步进为1Hz的矩形波波形。通过把数据写入24C04可以实现掉电保护功能。经实际测测试完成了题目要求的全部功能和指标。 一、系统方案 1.1比较与选择 方案一:采用DDS专用芯片AD9850作为信号产生模块,以单片机为系统的控制核心。该方案具有频谱纯度高、集成度高等特点。由于AD9850自带32位相位累加的数控振荡器,会产生低噪声、高稳定的频率输出波形。但它只直接提供了实现多种数字调制的功能,像二进制PSK、二进制FSK,这类调制方式实现起来比较简单,二要实现模拟线性调制FM具有一定的难度。故此方案也不采用。 方案二:采用基于FPGA的直接数字频率合成,并以FPGA作为整个系统的信号产生和控制中心。基于FPGA的直接数字频率合成其组成框图如图1-1。直接数字频率合成(DDS),具有频率切换速度快,频率分辨率高、可编程全数字化、相位连续、转换速度高、控制方便且有输出任意波形的能力等优点。用FPGA实现DDS技术比较灵活,可以产生多种调制方式,多种组合方式。采用此方案把重心放在了FPGA设计上,增加了FPGA部分程序的量,鉴于分工关系,放弃此方案。  图1-1 基于FPGA的直接数字频率合成 图1-1 基于FPGA的直接数字频率合成 方案三:采用基于DDS专用芯片AD9850作为信号产生模块,并以基于ARM7的微控制器ARM1138作为整个系统的控制核心。在ARM1138中嵌入UCOSII操作系统方便实现多任务处理。例如波形转换,频率调节,幅值调节,12864显示,I2C掉电保护等。本方案融合了如方案一频率合成的优点,并能发挥ARM控制器强大的系统管理能力。同时可利于分工合作,以最快的时间完成题目的所有要求。此方案比较灵活、可扩展性好,能完全达到设计要求,故采用此方案。

二、理论分析与说明 2.1总体设计思路及说明 ARM微控制器从键盘获得控制信息,通过计算得到控制字并通过IO口送给DDS的频率和相位的控制端口,同时,将信息显示在LCD上。DDS输出信号由程序控制其预置频率和相位的正弦信号或方波信号,再通过放大倍数可调的运算放大系统来控制调幅。三角波则由方波信号经过一级方大后通过积分电路获得。掉电保护功能则由ARM1138内部AD把数据读回再通过I2C写入24C04来完成。结构图如图2-1。

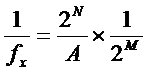

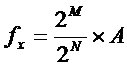

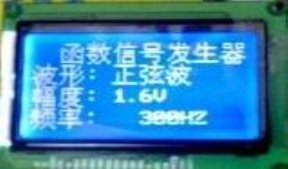

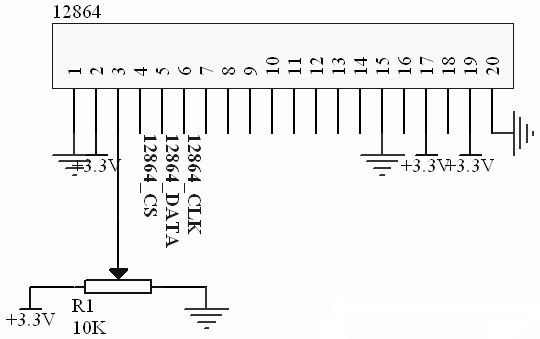

图2-1 基于ARM1138的直接数字频率合成 2.2DDS的实现设计 DDS的基本原理是利用采样定理,通过查表法产生波形,其基本架构如图2-2所示: 图2-2 DDS原理框图 相位累加器由N位加法器与N位累加寄存器级联构成。 每来一个时钟脉冲fs,加法器将频率控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。 由此可以看出, 相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。 用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值 (二进制编码) 经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。 DDS在相对带宽、频率转换时间、高分辨力、相位连续性、 正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。 DDS原理有以下特点: (1)输出频率相对带宽较宽 输出频率带宽为50%fs(理论值)。但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制, 实际的输出频率带宽仍能达到40%fs。 (2)频率转换时间短 DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。事实上,在DDS的频率控制字改变之后,需经过一个时钟周期之后按照新的相位增量累加,才能实现频率的转换。因此,频率转换的时间等于频率控制字的传输时间,也就是一个时钟周期的时间。时钟频率越高,转换时间越短。DDS的频率转换时间可达纳秒数量级,比使用其它的频率合成方法都要短数个数量级。 (3)频率分辨率极高 若时钟fs 的频率不变,DDS的频率分辨率就由相位累加器的位数N决定。 只要增加相位累加器的位数N即可获得任意小的频率分辨率。目前,大多数DDS的分辨率在1Hz数量级,许多小于1mHz甚至更小。 (4)相位变化连续 改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。 (5)输出波形的灵活性 只要在DDS内部加上相应控制如调频控制FM、 调相控制PM和调幅控制AM,即可以方便灵活地实现调频、调相和调幅功能,产生FSK、PSK、ASK和MSK等信号。另外,只要在DDS的波形存储器存放不同波形数据, 就可以实现各种波形输出, 如三角波、锯齿波和矩形波甚至是任意的波形。当DDS的波形存储器分别存放正弦和余弦函数表时,既可得到正交的两路输出。 分析计算 假设时钟为2MHz,数据保持寄存器选择N Bit,在时钟驱动下,累加器输出结果S被反馈到累加器输入端B,B和A的数据被累加到S,下一个时钟脉冲又将S反馈到B,再次与A累加到S,下一个时钟脉冲又将S反馈到B,如此循环累加,实现按步进值,按时钟节拍循环累加,使得N Bit数据被徐循环累加,产生循环扫描的地址码0~64(高6 Bit)。完成一次地址循环需要的时间由时钟和步进值决定,可以由公式计算: 一次地址循环可以输出一个完整的波形,既T就是输出波形的周期,转换成频率 ,得到计算公式: ,得到计算公式:  , ,  当晶振(2M)和计数器Bit数N确定之后, 既与步进值A成正比,对A的调整可以完成对 既与步进值A成正比,对A的调整可以完成对 的设定,当N足够大时,比例常数 的设定,当N足够大时,比例常数 可以很小,例如0.01,既 可以很小,例如0.01,既 等于A的0.01倍,这样就可以实现对 等于A的0.01倍,这样就可以实现对 的精细调整,譬如0.01Hz。 的精细调整,譬如0.01Hz。 根据题目的基本要求,频率范围为100HZ~20KHZ。 根据:输出频率: 最小频率分辨率: 其中m为相位累加器的位数,FTW为频率控制字, 为时钟频率,输出信号频率主要取决于频率控制字FTW.当N增大时, 为时钟频率,输出信号频率主要取决于频率控制字FTW.当N增大时,  可以不断增加, 可以不断增加, 2.3正弦波产生模块实现原理 由DDS原理,AD9850有40位控制字,32位用于频率控制,5位用于相位控制。1位用于电源休眠(Power down)控制,2位用于选择工作方式。这40位控制字可通过并行方式或串行方式输入到AD9850,图4是控制字并行输入的控制时序图,在并行装入方式中,通过8位总线A0…D7将可数据输入到寄存器,在重复5次之后再在FQ-UD上升沿把40位数据从输入寄存器装入到频率/相位数据寄存器(更新DDS输出频率和相位),同时把地址指针复位到第一个输入寄存器。接着在W-CLK的上升沿装入8位数据,并把指针指向下一个输入寄存器,连续5个W-CLK上升沿后,W-CLK的边沿就不再起作用,直到复位信号或FQ-UD上升沿把地址指针复位到第一个寄存器。在串行输入方式,W-CLK上升沿把25引脚的一位数据串行移入,当移动40位后,用一个FQ-UD脉冲即可更新输出频率和相位。图2-3是相应的控制字串行输入的控制时序图。 图2-3 DDS电路实现原理图如图2-4所示: 本次设计我们采用的是8位并行数据线控制,所用到的引脚功能如下: D0~D7:8 位数据输入口,可给内部寄存器装入 40 位控制数据。 FQ-UD:频率更新控制信号,时钟上。 W-CLK:字装入信号,上升沿有效。 RESET:复位端。低电平清除 DDS 累加器。 图2-4 2.4方波模块实现原理 AD9850可以产生一个频谱纯净、频率和相位都可编程控制且稳定性很好的模拟正弦波,这个正弦波能够直接作为基准信号源,或通过其内部高速比较器转换成标准方波输出,直接产生方波,这个是DDS合成的最大优点。 2.5三角波模块实现原理 由矩形波放大后经积分电路转换实现。由于积分电容的影响,输出的三角波有失真,所以使用一个四位拔码开关,选取不同的积分电容,选取不同的频率范围。 积分模块原理:在本设计电路中,三角波是通过反向积分器对方波的积分产生。积分器的设计就是选择集成运算放大器和计算确定外电路的元件参数。应注意到设计积分电路还应考虑的问题是怎样减小积分漂移来减小积分误差。 (1)集成运放的选择:在本设计中,集成运放选用NE5532,因其有较小的输入失调电压和输入失调电流,且开环增益和带宽足够。 (2)电路元件参数的确定和电路原理图如图2-5所示: 、信号输入端接入一耦合电容,大小为10uF; 、如图(1)所示,左边的NE5532为运算放大电路,先将方波的V-PP放大到20V再进行积分,放大倍数计算为A=R2/R1。R3为静态平衡电阻,用以补偿偏置电流所产生的失调。R4为积分漂移泄放电阻,用以防止积分漂移所造成的积分饱和或截止现象,但是,增加R4后,由于R4对电容的分流作用,会产生新的积分误差,所以应使R4>>RC,一般选择R4=10R3。 、积分时间常数て的确定:积分设计常数て是决定积分器工作速度的主要参数,て越小工作速度越高。但由于集成运放的最大输出电压为有限值,是不允许将时间常数选得太小。如果集成运放的最大输出电压为Vom,方波电压幅值为E,则:て的值必须满足 即  若て太大,积分器的输出就小;て太小集成运放的输出就饱和。而且て的选择与信号频率有关,频率越低,时间常数就应越大。 、积分电容的确定:て确定后,根据て=RC,则可得出积分电容的大小。一方面,增大输入电阻R可以减小积分电容,但这又会加剧积分漂移;另一方面,积分电容越大漏电也会增大,使积分误差增大。所以在选择时应对其进行综合考虑。 经计算和实验,本设计要求的频率范围从100Hz—20KHz的方波积分成三角波只需要一个105和一个273的两种不同的瓷片电容即可达到。此装置再换上不同的电容输出的三角波频率范围可达10HZ到1MHZ。 图2-5 2.6幅值调节模块 由于AD9850输出的正弦信号只有固定幅值,无法满足幅值可调 因此利用可编程放大器实现幅值控制 因此利用可编程放大器实现幅值控制 但这种方法只能实现倍数调节,而无法实现高精度连续调节 但这种方法只能实现倍数调节,而无法实现高精度连续调节 本设计正弦幅值控制要求必须连续可调,要高精度,X9511数字电位器的特点是只要按下向上按输入(PU)和向下按输入(PD)即可实现电阻可调,其原理图如2-6所示: 本设计正弦幅值控制要求必须连续可调,要高精度,X9511数字电位器的特点是只要按下向上按输入(PU)和向下按输入(PD)即可实现电阻可调,其原理图如2-6所示: 图2-6 因此,我们采用了数字电位器X9511,外加两个按键进行电阻的输出可调,改变放大器的反馈电阻,从而达到改变放大倍数,即实现了幅值可调。其电路原理图如图2-7所示: 图2-7 2.7显示模块设计 本次设计的显示我们用的是12864液晶,12864液晶相对于1602液晶显示的内容要丰富得多,显示的信息量大,切换全部用微动开关作按键来完成。液晶自带字库,显示汉字和符号方便。该液晶屏能显示4行字符,每行显示8个汉字或者16个英文字符,显示的信息量已经足够。它的接口有20根线,有串行控制和并行控制两种驱动方式,在这里使用串行控制,以节省IO口,图2-8为液晶接口电路。图中的R1为液晶显示对比度的调节电阻,典型值为10K,液晶选用3线串口驱动,这样的好处是减少IO口的使用,这3跟线分别为时钟线(12864_CLK)、片选线(12864_CS)、数据线(12864_DATA)。

本次我们用了5个按键控制,KEY1是选择波形型号,KEY2选择频率递增,KEY3选择频率递减,KEY4选择幅值递增,KEY5选择幅值递减。详细见程序流程图控制。

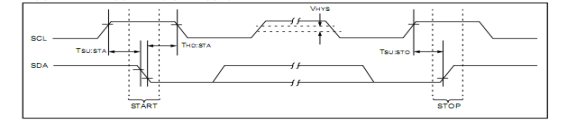

图2-8 液晶接口电路 2.8 掉电保护I2C模块设计 掉电保护我们采用的是24C02芯片,此芯片有2K的CMOS的E2PROM。24C02的 400KHz I2C 总线协议兼容 1.8 到 6.0 伏工作电压范围低功耗 CMOS技术写保护功能,当 WP 为高电平时进入写保护状态,可以定时编程擦写1,000,000 可保存数据可保存100年。24C02的时序如图2-9所示:

三、程序设计图2-9 本次软件设计流程如图3-1所示:程序初始化后进入初始界面,再判断KEY1是否被按下,按下KEY1是选择波形型号,按下KEY2选择频率递增,按下KEY3选择频率递减,按下KEY4选择幅值递增,按下KEY5选择幅值递减。本设计最大的优点就是能实现掉电保护,实时保存数据,防止电压过低或者突然断电造成的数据丢失。 图3-1 四、系统测试 4.1测试条件 表1 仪器仪表

4.2测试方案与测试结果 4.2.1观察示波器,记录频率值和输出电压峰-峰值。 表二 频率值和输出电压峰-峰值测量记录表

4.2.2 观察示波器,记录步进频率值。 表三 步进频率值记录表

4.3测试结果分析 由实验调试结果及测试结果,该函数信号发生器达到了题目的所有指示要求,在选择波形与调节幅度频率试时采用LCD人机交互界面,界面友好方便,具有直观性。 五、结语 本次设计的低频三相信号源,主要运用了DDS基本原理,利用ARM1138作为仿真测试和实际测量(测量结果见上表)符合题目给定的基本要求。 六、参考文献 [1].谢自美,电子线路设计、试验、测试,武汉:华中科技大学出版社,2002年,第二版; [2].黄志伟,全国大学生电子设计竞赛训练教程,北京:电子工业出版社,200年 [3].康华光,电子技术基础.模拟部分,北京:高等教育出版社,1999年,第四版 附录 1.程序压缩包 2.附图

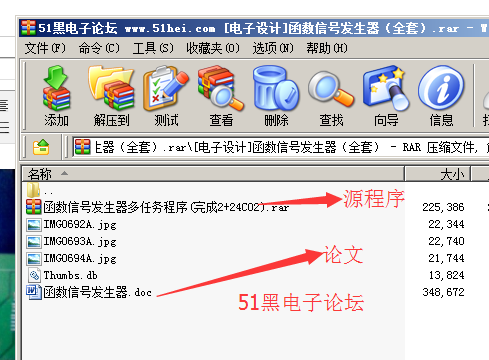

全部资料下载地址:

http://www.51hei.com/bbs/dpj-93416-1.html

|