- PL端接入CameraLink相机,通过Base模式采集图像(1280*1024),然后通过VDMA缓存到PS端DDR。

- 使用AXI4-Stream Switch IP核将图像复分成两路,一路用于边缘检测处理(Sobel算法),另一路直接回显。

- 利用Video Mixer IP核将图像叠加,通过HDMI输出原始图像或者算法处理后的图像。本案例支持CameraLink Base/Full模式、彩色/黑白相机。

此开发详解基于创龙ZYNQ Z-7045/Z-7100评估板TLZ7xH-EVM展开。 增加TLZ7xH-EVM视频播放框

2.案例框图 3.申请IP核license 本开发案例使用的Video Mixer和Chroma Resampler IP核,需要到官网下载IP核免费license,否则将无法通过TcL脚本生成Vivado工程。 请参照创龙TLZ7xH-EVM评估板(ZYNQ Z-7045/Z-7100)用户手册《Xilinx Vivado 2017.4及License安装教程》文档,导入IP核。 成功导入后,点击View License Status可以查看新添加的IP核license如下图。 4.Vivado工程说明 参照创龙TLZ7xH-EVM评估板(ZYNQ Z-7045/Z-7100)《基于TcL脚本生成Vivado工程及编译》文档,使用TcL脚本生成Vivado工程。 (1)生成评估板TLZ7xH-EVM、ZYNQ型号为xc7z100的Vivado工程: Vivado# vivado -mode batch -source tl_cameralink_edge_display_project.tcl -tclargs tlz7xh-evm xc7z100ffg900-2 (2)生成评估板TLZ7xH-EVM、ZYNQ型号为xc7z045的Vivado工程: Vivado# vivado -mode batch -source tl_cameralink_display_project.tcl -tclargs tlz7xh-evm xc7z045ffg900-2 进入Vivado工程所在的runs路径,双击.xpr文件打开工程。 点击"IP INTEGRATOR -> Open Block Design",打开Vivado工程如下图所示。 点击Address Editor选项,可以看到IP核分配的地址,在PS端可以通过配置这些地址(寄存器)来控制IP核。 5.IP核与模块简介 lvds_n_x_1to7_sdr_rx模块 源码路径:hw\src\hdl\lvds_n_x_1to7_sdr_rx.v 模块实现了将差分输入数据转化成并行数据,参考时钟delay_refclk_in需接200MHz或者300MHz,本例程使用PS端的200MHz的FCLK1。双击打开配置界面。参数N表示通道数,X表示每个通道的数据差分对数量。 根据CameraLink V2.0标准: - Lite/Base模式:单通道,每通道数据差分对为4对,需要1个连接器。

- Medium模式:双通道,每通道数据差分对为4对,需要2个连接器。

- Full/80bit模式:三通道,每通道数据差分对为4对,需要2个连接器。

配置N=1表示使用Base模式,N=2为Medium模式,N=3为Full模式。X固定为4。更详细的说明请查阅文档xapp585-lvds-source-synch-serdes-clock-multiplication.pdf。 cameralink_bit_allocation_rx模块 源码路径:hw\src\hdl\cameralink_bit_allocation_rx.v 功能:将lvds_n_x_1to7_sdr_rx模块Serdes串并转换出来的数据进行重组,分离出行同步信号、场同步型号、数据有效信号和每个像素数据。参数N表示通道数量和lvds_n_x_1to7_sdr_rx模块功能一致。 - N=1,Base模式,输出端PortA、PortB、PortC有效。

- N=2,Meduim模式,输出端PortA、PortB、PortC、PortD、PortE、PortF有效。

- N=3,Full模式,输出端PortA、PortB、PortC、PortD、PortE、PortF、PortG、PortH有效。

关键代码解释:

- data_in的数据排列格式(lvds_n_x_1to7_sdr_rx模块串转并后的数据)。

lvds_n_x_1to7_sdr_rx模块将每一对数据差分对转换后的数据如下(XAPP585文档):

CameraLink(LVDS视频)协议标准如下图所示。

结合CameraLink(LVDS视频)协议标准,得出4对数据通道转换后的数据在data_in数据的排列顺序如下。

2.分离出行场同步信号、数据有效信号和像素数据。

根据CameraLink协议: - RX24对应行有效信号LVAL(行同步信号)。

- RX25对应帧有效信号FVAL(场同步信号)。

- RX26对应数据有效信号DVAL。

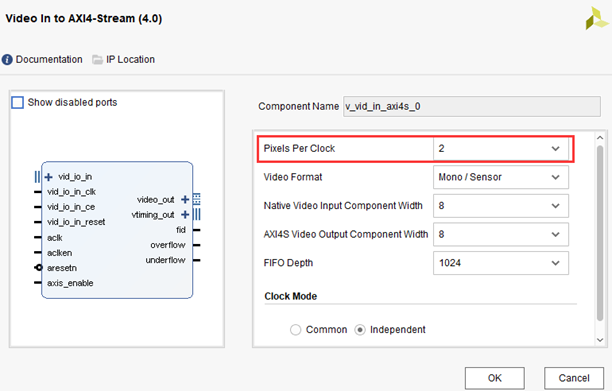

其他对应关系如下图: 因此,根据上图即可将各信号分离出来。 Video In to AXI4-Stream IP核 Video In to AXI4-Stream IP核配置为Mono/Sensor视频格式,Base模式2 pixels per clk,每个色彩数据位宽为8bits。关于IP核的详细技术说明可以查看《pg043_v_vid_in_axi4s.pdf》文档。

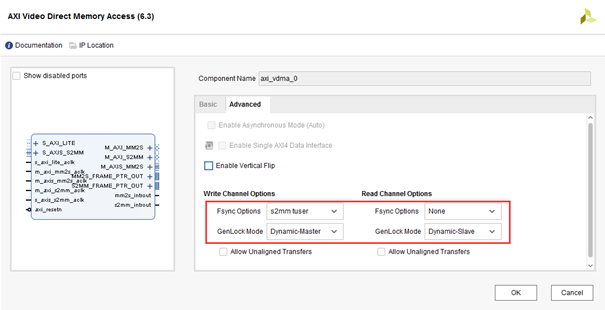

VDMA(AXI Video Direct Memory Access) IP核 VDMA IP核技术说明文档为《pg020_axi_vdma.pdf》。S2MM是将视频流传到DDR中,MM2S是从DDR中把图像数据传输出去。配置如下图所示。

配置VDMA为读写跟随模式。

AXI4-Stream Subset Converter IP核 实现功能:Y转RGB。

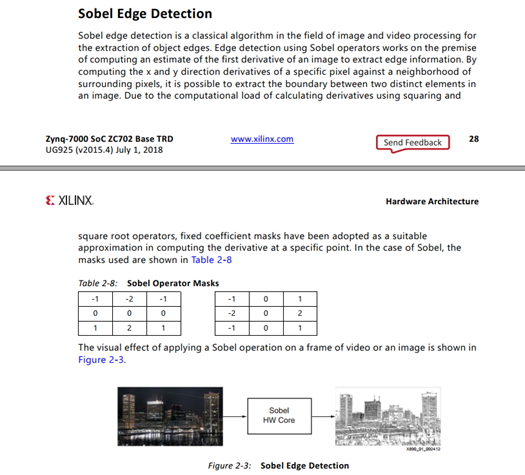

AXI4-Stream Switch IP核 实现功能:将图像复分成两路,一路用于边缘检测处理(Sobel算法),另一路直接回显。 YCrCb to RGB Color-Space Converter IP核 实现功能:RGB转YCrCb444。 Chrome Resampler IP核 实现功能:YCbCr444转YCbCr422,输入24位YCbCr444数据,输出16位YCbCr422数据。 Image_filter IP核 Image_filter IP核源码是基于Xilinx的xapp1167的Sobel边缘检测算法例程,对应的HLS源码在FPGA-HLS-demos目录下,技术说明文档为《ug925-zynq-zc702-base-trd.pdf》。

《ug925-zynq-zc702-base-trd.pdf》文档附录A:Register Description -> Sobel Filter Registers小节有相关寄存器说明 - 寄存器0x00:控制和状态寄存器,可控制IP核的停止和启动

- 寄存器0x14:设置图像的行数(最大支持1920x1080)

- 寄存器0x1c:设置图像的列数

- 寄存器0xb4:Sobel滤波的高阈值

- 寄存器0xbc:Sobel滤波的低阈值

- 寄存器0xc4:反转Sobel滤波器的输出(黑白反转)

寄存器的定义也可以可查看以下文件:ip_package/xilinx_com_hls_image_filter_1_0/drivers/image_filter_v1_0/src/ximage_filter_hw.h Video Mixer IP核 Video Mixer IP核可以对多路视频进行叠加输出,为OSD IP的升级版,功能和OSD相似。本例程的作用为,将相机输入的图像,通过Mixer IP核叠加到1920*1080的视频中,最终通过HDMI输出显示。需要通过PS端,配置寄存器使能Mixer。

AXI Uartlite IP核 用于和CameraLink相机通信,PS端可通过该接口对CameraLink相机进行配置(分辨率、Base/Full模式等功能)。具体说明请参考pg142-axi-uartlite.pdf。 Video Timing Controller IP核 Video Timing Controller IP核用于产生分辨率为1080P60的时序,用于HDMI输出,关于IP核的详细技术说明可以查看《pg016_v_tc.pdf》文档。双击Vivado工程v_tc IP核框图。在弹出的界面,点击"Default/Constant",可以看到已将Video Timing Controller IP核配置成1080P60的时序,如下图所示。 AXI-Stream to video out IP核 AXI-Stream to video out IP核配置视频格式为RGB,1 pixels per clk,每个色彩数据位宽为8bits。关于IP核的详细技术说明可以查看《pg044_v_axis_vid_out.pdf》文档。双击v_axi4s_vid_out IP核框图,查看IP核具体配置如下图。

Clocking Wizard IP核 配置一路148.5MHz的时钟,用于HDMI输出。该时钟对应的是1080P60的像素时钟。 若输入其他分辨率的视频,则需要修改VDMA IP核中图像大小的配置、Video Timing Controller IP的时序和Clocking Wizard IP核输出的像素时钟。 6.案例演示 实验硬件说明 CameraLink相机参考型号: - 彩色RS-A5241-CC107-S00,支持Full/Base,分辨率2560*2048,帧率107Hz

- 黑白RS-A5241-CM107-S00,支持Full/Base,分辨率2560*2048,帧率107Hz

参考下表和图将相机接到评估板CameraLink接口,显示器接到HDMI OUT接口。

模式 | 接口(相机-评估板) | Base | CL0-CON18 |

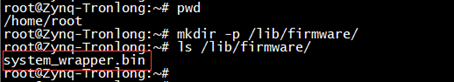

基于Linux系统测试 评估板上电启动进入文件系统,执行如下指令新建一个"/lib/firmware"文件夹。将由Vivado工程编译生成的xxx.bin文件传送到评估板文件系统的"/lib/firmware/"目录下,并重命名为system_wrapper.bin。 参考创龙TLZ7xH-EVM评估板(Z-7045/Z-7100)用户手册《生成PL设备树及动态加载PL程序和设备树》文档,生成设备树,然后将编译好的dtbo文件拷贝到文件系统"lib/firmware"目录下。 Target# mkdir -p /lib/firmware/

HDMI OUT芯片接的是PS端的I2C,需要加载PS端设备树,加载成功后如下图所示。 Target# mkdir /configfs

Target# mount -t configfs configfs /configfs

Target# mkdir /configfs/device-tree/overlays/full

Target# echo -n zynq-zc706-overlay.dtbo > /configfs/device-tree/overlays/full/path 再加载PL端程序和设备树。可以看到AXI UART对应的节点为/dev/ttyUL1。 Target# mkdir /configfs/device-tree/overlays/cameralink

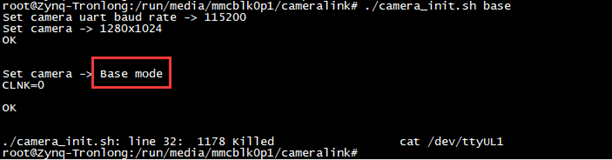

Target# echo -n "pl.dtbo" > /configfs/device-tree/overlays/cameralink/path 将例程image目录下的脚本拷贝到文件系统,执行脚本进行配置,即可在显示器看到相机采集的视频。 Target# ./camera_init.sh base //初始化CameraLink相机

脚本说明: Target# ./sil9022_i2c_1080p.sh //初始化HDMI OUT

Target# ./axi_vdma_cameralink.sh //初始化VDMA

Target# ./switch_video.sh 1 //配置AXI4-Stream Switch IP核,参数1为原始图像

Target# ./mixer_init.sh 1 //初始化Video Mixer IP核,参数1为原始图像

Target# ./sobel_filter_init.sh //初始化Image_filter IP核 Target# ./mixer_init.sh 2 && ./switch_video.sh 2 //切换到算法处理后的图像 对于RS-A5241的相机,Base模式下,1280*1024的分辨率状态下,图像帧率有120+帧,所以图像曝光短,图像较暗,增大Image_filter IP的阈值可以获得更好的效果。 Target# devmem 0x43c000b4 w 0xff //设置高阈值为0xff Target# devmem 0x43c000bc w 0xa0 //设置低阈值为0xa0 设置颜色反转: Target# devmem 0x43c000c4 w 1 //0xc4寄存器设置为1,边缘为白色,若为0;边缘为黑色

|