这是之前做的一次设计,所有资料都是自己找的,自己想办法做出来的。

- 学习运用LM358芯片设计直流稳压电源。

- 基于74LS160自主设计一个51秒定时电路,学会对计数器芯片的应用。

- 学习运用NE555设计多谐振荡器。

- 学习运用共阴极七段显像管。

- 学习蜂鸣器的运用

设计具有手控方式实现体育竞赛秒级定时的电路,利用LED数码管显示计数器的值。掌握用 “反馈置数法”构成定时电路的设计方法;用Multisim软件画图仿真;用Protel软件绘制PCB板图。具体要求如下: (1)设计一个计时电路,定时时间为(20+学号末两位)秒,并能实时显示时间; (2)设置操作开关控制计时器的清零、启动和暂停/连续计时; (3)要求定时电路递增计时,每隔一秒钟,定时电路加1; (4)当计时电路递增计时到预定数值时发出报警信号; (5)外界供电为AC 220市电,设计能满足定时电路供电要求的电源。

图1 51秒定时器原理框图 30 秒定时器主要由秒脉冲发生器、 控制电路、 计数器、译码显示器电路和报警电路五部分组成。 电路原理分析: - 市交流电220V从T1变压器进入降压到适合大小的交流电。

- 减压后的交流电经过四个二极管组成的整流电路,将极性变化的交流电转变为极性单一的脉动直流电。

- 经过电解电容C3和瓷片电容C4组成的滤波电路滤除整流后脉动电压中的交流成分,将脉动的直流电转变为平滑的直流电。

- 在经过后面四个二极管和LM358P运放和达林顿管组成一个稳压电路,将平滑的直流电转变为稳定的直流电,使其基本不受电网电压波动和负载电阻变化的影响。

- 通过调节电位器R3的阻值,将输出的电压调节到5V

图2 电源电路仿真电路

图3 电压表示数

它由分压器、比较器、基本 R--S 触发器和放电三极管等部分组成。分压器由三个 5 KΩ的等值电阻串联而成。分压器为比较器  、  提供参考电压,比较器  的参考电压为  ,加在同相输入端, 比较器  的参考电压为  ,加在反相输入端。 比较器由两个结构相同的集成运放  组成。 高电平触发信号加在  的反相输入端,与同相输入端的参考电压比较后,其结果作为基本 R--S 触发器  端的输入信号;低电平触发信号加在  的同相输入端,与反相输入端的参考电压比较后,其结果作为基本 R—S 触发器  端的输入信号。基本 R--S 触发器的输出状态受比较器  的输出端控制。

图4 555定时器

由 555 定时器组成的多谐振荡器如图所示,其中 R 1 、R 2 和电容 C 为外接元件。其工 作波如图所示。设电容的初始电压  =0, t=0时接通电源,由于电容电压不能突变,所以高、低触发端  =  =0<  ,比较器  输出为高电平,  输出为低电平,即  ,  (1 表示高电位, 0 表示低电位) , R S 触发器置1, 定时器输出  此时  ,定时器内部放电三极管截止,电源V cc经  向电容C充电,逐渐升高。当  上升到  时,  输出由0翻转为1, 这时  , R—S 触发顺保持状态不变。 所以 0<t<  期间,定时器输出  为高电平1。  时刻,  上升到  ,比较器  的输出由1变为0, 这时  , R -S触发器复0,定时器输出  。  期间,  ,放电三极管T导通, 电容C通过R 2放电。  按指数规律下降,当  时比较器  输出由0变为1,R-S触发器的  ,Q的状态不变,  的状态仍为低电平。  时刻,  下降到  ,  比较器输出由 1 变为 0,R---S 触发器的,  触发器处于 1,定时器输出  。此时电源再次向电容 C 放电,重复上述过程。 通过上述分析可知,电容充电时,定时器输出  ,电容放电时,  ,电容不断地进行充、放电,输出端便获得矩形波。多谐振荡器无外部信号输入,却能输出矩形波,其实质是将直流形式的电能变为矩形波形式的电能.

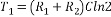

由图可知,振荡周期  。  为电容充电时间,  为电容放电时间。 充电时间  放电时间  矩形波的振荡周期  矩形波频率  计算:

图5 1HZ多谐振荡器仿真电路

- 基于74LS160计数器设计51秒定时器(可通过开关控制计时器的清零、启动和暂停/连续计时;)

74LS160 的清除端是异步的。当清除端CLR为低电平时,不管时钟端CLK状态如何,即可完成清除功能。 74LS160 的预置是同步的。当置入控制器LOAD为低电平时,在 CLK上升沿作用下,输出端 Q0-Q3 与数据输入端 D0-D3 一致。对于74LS160,当 CLK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,则LOAD应避免由低至高电平的跳变,而 74LS160 无此种限制。 74LS160 的计数是同步的,靠CLK同时加在四个触发器上而实现的。当ENP、ENT均为高电平时,在CLK上升沿作用下 Q0-Q3同时变化,从而消除了异步计数器中出现的计数尖峰。对于74LS160,只有当CLK为高电平时,ENP、ENT才允许由高至低电平的跳变, 而74LS160的 ENP、ENT跳变与CLK无关。160 有超前进位功能。当计数溢出时,进位输出端(RCO)输出一个高电平脉冲,其宽度为 Q0的高电平部分。 在不外加门电路的情况下,可级联成 N位同步计数器。对于74LS160,在CLK出现前,即使 ENP、ENT、CLR发生变化,电路的功能也不受影响。

图6 74LS160封装图 图7 74LS160逻辑图

表1 74LS160的功能表

表2 引出端符号意义

如图所示,51秒定时器计数器设计电路如下: 51进制设计:U1为十位数部分,U2为个位数部分。当ENP (U2)=ENT (U2)=CLR(U1、U2)=1时,计数器开始加法计算,由00不断加法计算到51秒。RCO(U2) 连接ENP、ENT(U1),当U2的计数器一个循环后,U1的示数加1,由三脚与非门U7A连接U1的QA和QC,U2的QA,当输出计数器输出了51时,U7A与非门输出低电平,S1继电器切换电路到地,计数器暂停在51,经过U8A非门后,输出高电平,蜂鸣器鸣叫。 开启:开关S2控制计数器开启。当S2断开时,ENP (U2)=ENT (U2)=CLR(U1、U2)=1,计数器启动。当S2连接时,CLR(U1、U2)=0,电路关闭。 置0:电路正常运行时,当S2、S3断开,S4连接,计数器置0。 暂停/继续:电路正常运行时,当S2、S4断开,S3连接,计数器保持状态,当S4连接时,计数器继续运行。

图8 两片74LS160 芯片设计51秒定时器的计数器部分 - 基于74LS48驱动共阴极七段显像管的显示电路设计

- 计数器实现了对时间的累计以 8421BCD 码形式输出,译码驱动电路将计数器输出的8421BCD 码转换为数码管需要的逻辑状态, 并且为七段数码管的正常工作提供足够的工作电流。译码器是一个多输入、多输出的组合逻辑电路。它的工作是把给定的代码进行“翻译” ,变成相应的状态, 使输出通道中相应的一路有信号输出。 译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数字分配,存储器寻址和组合控制信号等。译码器可以分为通用译码器和显示译码器两大类。用于驱动 LED 七段数码显示常用的有74LS48。

- 译码器 74LS48

74LS48 是 BCD-7 段译码器/驱动器,其输出是OC门输出且高电平有效, 专用于驱动 LED七段共阴极显示数码管。其功能是把输入的 8421BCD 码 ABCD 译成七段输出 a-g,再由七段数码管显示相应的数。由 74LS48 和 LED 七段共阴极数码管组成一位数码显示电路。若将个位、时位、百位计数器的输出分别接到相应七段译码器的输入端,便可进行不同数字显示。在译码器输出与数码管之间串联的 R 为限流电阻。当计数器在 CP 脉冲的作用下,就应将其状态显示成清晰的数字符号。74LS48 的管脚如图所示。在管脚图中,管脚 LT、RBI、BI/RBO 都是低电平是起作用,作用分别为: LT 为灯测检查,用 LT 可检查七段显示器个字段是否能正常被点燃。 BI 是灭灯输入,可以使显示灯熄灭。 RBI 是灭零输入, 可以按照需要将显示的零予以熄灭。 BI/RBO 是共用输出端, RBO 称为灭零输出端,可以配合灭零输出端 RBI,在多位十进制数表示时,把多余零位熄灭掉,以提高视图的清晰度。

图9 74LS48管脚图

- 74LS48 的功能: 74LS48的功能表如表所示。

表3 74LS78芯片功能表

(1)译码功能:将 LT,RBI 和 BI/RBO 端接高电平,输入十进制数 0~9的任意一组 8421BCD码(原码),则输出端 a~g也会得到一组相应的 7 位二进制代码( 74LS48 驱动共阴极,输出3FH、06H、5BH, ; 74LS47驱动共阳极,输出 COH、F9H、A4H, )。如果将这组代码输入到数码管,就可以显示出相应的十进制数。 (2)试灯功能:给试灯输入加低电平,而 BI/RBO 端加高电平时,则输出端 a~g均为高电平。若将其输入数码管,则所有的显示段都发亮。此功能可以用于检查数码管的好坏。 (3)灭灯功能:将低电平加于灭灯输入时,不管其他输入为什么电平,所有输出端都为低电平。将这样的输出信号加至数码管,数码管将不发亮。 (4)动态灭灯功能:RBI 端为灭零输入端,其作用是将数码管显示的数字 0熄灭。当RBI=0,且 DCBA=0000 时,若 LT=1,a~g输出为低电平,数码管无显示。利用该灭零端,可熄灭多位显示中不需要的零。不需要灭零时, RBI=1。

图10 显示部分仿真电路图 报警电路设计:由一个非门与蜂鸣器组成报警电路,当计数器达到51时,UA7输出低电平,通过非门U8A变成高电平,蜂鸣器工作,发出警报。

图11 报警电路设计电路图 总电路如下:上部分为直流稳压电源,通过调节电位器,将市电220V转为直流电5V,再经过下面电路完成51秒定时器电路,完成整个电路设计。 在计数器达到51秒之时,蜂鸣器鸣叫,要关闭即切换S3,即清零计数器,再切换高电平即继续启动。 启动:S2,S3连接,S2断开,计数器启动。 停止:S2,S3, S2连接,计数器关闭。 置0:S2、S3断开,S4连接,计数器置0。 暂停:S2、S4断开,S3连接,计数器计数暂停。 继续:S2断开,S3、S4连接,计数器计数继续运行。

图12 51秒定时器设计总电路图(开启、置0、停止)

图13 PCB原理图

图14 PCB图

图15 PCB 3D视图

表3 元器件清单列表

通过这次对两位十进制计数器74LS160的设计与制作,我懂得了如何将自己所学的东西运用于实际电路中,掌握了功能电路的基本设计方法,学会了74LS160计数器的应用,加深了对时序电路的理解,同时也掌握了仿真软件的应用,能够对设计的电路进行仿真,从而验证电路的正确性。通过这次设计我还学会了通过图书馆书籍和互联网进行资料的收集,为以后的设计工作奠定基础。在不断地学习着数电知识,并且了解了很多芯片的使用,以及连接的方式,在PCB的设计和操作中不断地学到很多东西,也理解了很多数字电子技术的理论,实践了这些技术。

全部资料51hei下载地址:

51秒计数器.zip

(1.84 MB, 下载次数: 35)

51秒计数器.zip

(1.84 MB, 下载次数: 35)

|