|

ЪЕбщвЛ змЯпгыМФДцЦї

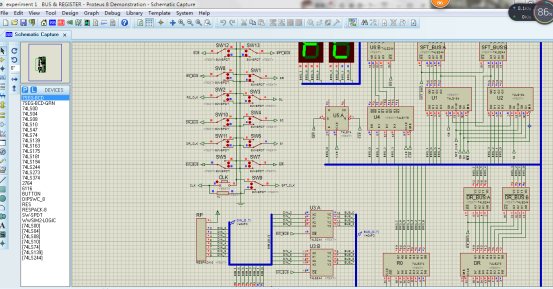

вЛЁЂЪЕбщФПЕФ 1ЁЂЪьЯЄЪЕбщШэМўЛЗОГЃЛ 2ЁЂеЦЮезмЯпвдМАЪ§ОнЭЈТЗЕФИХФюМАДЋЪфЬиадЃЛ 3ЁЂРэНтЫјДцЦїЁЂЭЈгУМФДцЦїМАвЦЮЛМФДцЦїЕФЙІФмЁЃ

ЖўЁЂЪЕбщФкШн 1ЁЂИљОнвбДюНЈКУЕФ8ЮЛЪ§ОнЭЈТЗЃЌЪьЯЄзмЯпСЌНгЕФЗНЗЈЃЌРэНт74LS244аОЦЌЕФзїгУЃЌРэНтИїЯрЙиаХКХдкЪ§ОнДЋЪфЙ§ГЬжаЦ№ЕФзїгУЃЛ 2ЁЂЭЈЙ§ВІТыПЊЙижУЪ§ЃЌНЋЪ§ОнДЋЫЭЕНИїМФДцЦїЃЌНЋМФДцЦїжаЪ§ОнЯдЪОГіРДЃЌЪьЯЄГЃгУЕФМФДцЦїЁЃ

Ш§ЁЂЪЕбщЦїМў 1ЁЂDДЅЗЂЦїЃЈ74LS74ЁЂ74LS175ЃЉЁЂШ§ЬЌЛКГхЦїЃЈ74LS244ЃЉЁЃ 2ЁЂМФДцЦїЃЈ74LS273ЁЂ74LS374 ЃЉКЭвЦЮЛМФДцЦїЃЈ74LS194ЃЉ

ЫФЁЂЪЕбщдРэ ЃЈМћЪЕбщжИЕМЪщЃЉ

ЮхЁЂЪЕбщВНжш зЂвтЃКЪЕбщЙ§ГЬжагІЙлВьзмЯпЩЯМАаОЦЌв§НХЩЯЯдЪОЕФЪ§ОнЕФБфЛЏЧщПіЃЌРэНтЪ§ОнДЋЫЭЕФЙ§ГЬКЭМФДцЦїДцЪ§ЃЌДгМФДцЦїЖСЪ§ЕФдРэЁЃ

ЪЕбщЃЈ1ЃЉВІТыПЊЙиЪфШыЪ§ОнжСзмЯп Ёё = = = = = = =1ЃЛЪжЖЏВйзїзмЯпDINЩЯЕФВІТыПЊЙиЃЌдкзмЯпDINЩЯжУЮЛЪ§Он0x55ЃЌЛКГхЦї244зшЖЯЁЃБШНЯзмЯпDINгыBUSзДЬЌЕФвьЭЌЁЃ =1ЃЛЪжЖЏВйзїзмЯпDINЩЯЕФВІТыПЊЙиЃЌдкзмЯпDINЩЯжУЮЛЪ§Он0x55ЃЌЛКГхЦї244зшЖЯЁЃБШНЯзмЯпDINгыBUSзДЬЌЕФвьЭЌЁЃ Ёё =0ЃЌБШНЯзмЯпDINгыBUSзДЬЌЕФвьЭЌЃЌМЧТМBUSзмЯпЕФЪ§ОнЃК =0ЃЌБШНЯзмЯпDINгыBUSзДЬЌЕФвьЭЌЃЌМЧТМBUSзмЯпЕФЪ§ОнЃК

ЪЕбщЃЈ2ЃЉDДЅЗЂЦїЪ§ОнЫјДцЪЕбщ Ёё =0ЃЌ =0ЃЌ = = = = =1ЃЛЭЈЙ§ВІТыПЊЙиИФБф74LS74ЕФDЖЫЃЈМДBUSзмЯпЕФBUS_0ЃЉЕФзДЬЌЃЌАДееЯТБэжУЮЛ74LS74ЕФ =1ЃЛЭЈЙ§ВІТыПЊЙиИФБф74LS74ЕФDЖЫЃЈМДBUSзмЯпЕФBUS_0ЃЉЕФзДЬЌЃЌАДееЯТБэжУЮЛ74LS74ЕФ ЖЫЁЂ ЖЫЁЂ ЖЫЃЌЙлВьВЂМЧТМCLKЖЫЩЯЩ§би ЁЂЯТНЕбиЬјБфЪБПЬQЖЫЁЂЖЫЕФзДЬЌЃЌЬюЙлВтНсЙћгкБэжаЁЃ ЖЫЃЌЙлВьВЂМЧТМCLKЖЫЩЯЩ§би ЁЂЯТНЕбиЬјБфЪБПЬQЖЫЁЂЖЫЕФзДЬЌЃЌЬюЙлВтНсЙћгкБэжаЁЃ

Ёё74LS175ЕФШ§ЬЌУХ244зшЖЯЃЈ =1ЃЉЃЌВІТыПЊЙижУЮЛBUSзмЯпЪ§ОнЃЌЪЙ74LS175ЕФDЖЫЗжБ№НгИпЃЌЕЭЕчЦНЃЌЙлВьВЂМЧТМЕБCLKЩЯЩ§би ЁЂЯТНЕбиЬјБфЪБQЖЫЁЂЖЫЕФзДЬЌЁЃ =1ЃЉЃЌВІТыПЊЙижУЮЛBUSзмЯпЪ§ОнЃЌЪЙ74LS175ЕФDЖЫЗжБ№НгИпЃЌЕЭЕчЦНЃЌЙлВьВЂМЧТМЕБCLKЩЯЩ§би ЁЂЯТНЕбиЬјБфЪБQЖЫЁЂЖЫЕФзДЬЌЁЃ ЁёЙлВь74LS175ЕФQЖЫЁЂЖЫКЭ74LS74ЕФQЖЫЁЂЖЫЕФвьЭЌЃЌЙлВьЕБ74LS175ЕФMRЖЫжУ0КѓЃЈ =0ЃЉЃЌЪфГіQЖЫЁЂЖЫЕФБфЛЏЁЃ =0ЃЉЃЌЪфГіQЖЫЁЂЖЫЕФБфЛЏЁЃ ЖМЪЧИпЕчЦНЃК1ЃЌ0ЃЌЕЭЕчЦНЃК0,1ЁЃЕБ74LS175ЕФMRЖЫжУ0КѓЃЈ =0ЃЉ ИпЕчЦНЃК1ЃЌ0ЃЌБфЮЊ0,1ЃЛЕЭЕчЦНЃК0,1ЛЙЪЧ0,1. =0ЃЉ ИпЕчЦНЃК1ЃЌ0ЃЌБфЮЊ0,1ЃЛЕЭЕчЦНЃК0,1ЛЙЪЧ0,1.

ЪЕбщЃЈ3ЃЉЭЈгУМФДцЦїЪЕбщ Ёё =0ЃЌ =0ЃЌ = = = = =1ЃЛВйзїВІТыПЊЙиЪфШыЪ§Он0xAA ЕНзмЯпЃЌЙлВтДЫЪБ74LS374КЭ74LS273ЪфГі6ЖЫQXЕФИїздзДЬЌЁЃ =1ЃЛВйзїВІТыПЊЙиЪфШыЪ§Он0xAA ЕНзмЯпЃЌЙлВтДЫЪБ74LS374КЭ74LS273ЪфГі6ЖЫQXЕФИїздзДЬЌЁЃ зДЬЌЃК 74LS374ЃК10101010 74LS273:00000000 Ёё74LS374ЕФCLKЖЫR0_CLKЩЯЩ§биЬјБфАбзмЯпЩЯЕФ0xAAЪ§ОнДцШыR0МФДцЦїЃЈ74LS374ЃЉЁЃ ЁёВІТыПЊЙиЕФШ§ЬЌУХ244зшЖЯЃЈ =1ЃЉЃЌЙлВьДЫЪБзмЯпBUSЩЯЕФзДЬЌЁЃ =1ЃЉЃЌЙлВьДЫЪБзмЯпBUSЩЯЕФзДЬЌЁЃ

змЯпBUSБЛзшЖЯЮоаХКХ

Ёё74LS374ЕФЪфГібЁЭЈЃЈ =0ЃЉЃЌЙлВтзмЯпBUSЕФзДЬЌЁЃ =0ЃЉЃЌЙлВтзмЯпBUSЕФзДЬЌЁЃ Ъ§ОнДгЮоБфЮЊoxAA

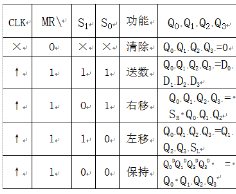

Ёё74LS273ЕФCLKЖЫDR_CLKЩЯЩ§биЬјБфАбзмЯпЩЯЕФ0xAAЪ§ОнДцШыDRМФДцЦїЃЈ74LS273ЃЉЁЃЙлВь74LS374КЭ74LS273ЪфГіЖЫQXЕФИїздзДЬЌЁЃ 74Ls374ЃК10101010 74LS273ЃК10101010 ЪЕбщЃЈ4ЃЉвЦЮЛМФДцЦїЪЕбщ Ёё =0ЃЌ =0ЃЌ = = = = =1ЃЛЭЈЙ§ВІТыПЊЙиЫЭШызмЯпBUSШЮвтАЫЮЛЖўНјжЦЪ§ЃЌИГжЕ74LS194ЕФЪфШыЖЫD0D1D2D3ЁЃЗжБ№ЩшжУ74LS194ЕФMRЖЫЁЂS1ЖЫЁЂS0 ЖЫЁЂSLЖЫЁЂSRЖЫЃЌЙлВьCLKЖЫЩЯЩ§би ЁЂЯТНЕбиЬјБфЪБПЬЪфГіЖЫQ0Q1Q2Q3ЕФзДЬЌЃЌбщжЄ74LS194ЕФЙІФмЁЃЙІФмБэШчЯТЃЌЦфжаЁАЁСЁБКХБэЪОЪфШыШЮвтжЕЁЃЙлВьЕчТЗжаСНИі74LS194СЊКЯЙЙГЩ8ЮЛвЦЮЛЦїЕФЗНЗЈЃЌМАвЦЮЛаЇЙћЁЃ =1ЃЛЭЈЙ§ВІТыПЊЙиЫЭШызмЯпBUSШЮвтАЫЮЛЖўНјжЦЪ§ЃЌИГжЕ74LS194ЕФЪфШыЖЫD0D1D2D3ЁЃЗжБ№ЩшжУ74LS194ЕФMRЖЫЁЂS1ЖЫЁЂS0 ЖЫЁЂSLЖЫЁЂSRЖЫЃЌЙлВьCLKЖЫЩЯЩ§би ЁЂЯТНЕбиЬјБфЪБПЬЪфГіЖЫQ0Q1Q2Q3ЕФзДЬЌЃЌбщжЄ74LS194ЕФЙІФмЁЃЙІФмБэШчЯТЃЌЦфжаЁАЁСЁБКХБэЪОЪфШыШЮвтжЕЁЃЙлВьЕчТЗжаСНИі74LS194СЊКЯЙЙГЩ8ЮЛвЦЮЛЦїЕФЗНЗЈЃЌМАвЦЮЛаЇЙћЁЃ 74LS194ЙІФмБэ

- DINзмЯпжаСЌНгзХВІТыПЊЙиЃЌдкbusзмЯпжаКЌгазХШ§ЬЌУХ

змЯпЩЯЕФЪ§ОнгЩDINзмЯпЩЯЕФВІТыПЊЙиПижЦ дкDINзмЯпЩЯДЋЪфЪ§ОнЕНbusзмЯпЃЌbusзмЯпДЋЪфЪ§ОнЕНЯдЪОЦСЩЯ ЭЌЃКDINзмЯпЩЯЕФЪ§ОнгыbusЩЯЕФЪ§ОнЖМЪЧЯрЭЌЕФ вьЃКвЛИізїЮЊЪфШыЃЌвЛИізїЮЊДЋЪф 2ЁЂДЅЗЂЦїЪЧЪБжгЩЯЩ§биЃЈЁќЃЉДЅЗЂЃЌЫВМфБЃДцЪ§ОнЃЛЫјДцЦїЪЧЪБжгИпЕчЦНЦкМфЪфГіИњЫцЪфШыБфЛЏЃЌЯТНЕбиЃЈЁ§ЃЉБЃДцЪ§ОнЁЃЖўепОЭЪЧДЅЗЂЗНЪНВЛЭЌЃЌЪЪгУгкВЛЭЌЕФГЁКЯЁЃШч CPU ИДгУзмЯпЕФЕижЗЫјДцОЭЪЧгУЫјДцЦїЁЃ

ЭъећЕФWordИёЪНЮФЕЕ51КкЯТдиЕижЗЃК

34_ЪЕбщвЛ.docx

(173.39 KB, ЯТдиДЮЪ§: 61)

34_ЪЕбщвЛ.docx

(173.39 KB, ЯТдиДЮЪ§: 61)

|

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664