项目分工:

1、领料、焊接、板子的成型。

2、板子的装接、调试。

3、程序的编写与仿真

4、资料的收集与整理、实验报告总结。

一、课题具体安排与实施实训时间:第十六周到第十九周;

第十六周收集材料,板子成型;

第十七周写程序;

第十八周调试、写实验报告;

第十九周答辩。

二、课题目标:1、掌握基于C51单片机、FPGA模数混合硬件系统设计和程序设计;

2、学会智能电子产品的功能设计与任务分析,能进行小型电子产品方案的设计;

3、通过智能循迹小车软件系统设计,整机调试,设计、软件性能并仿真调试;

4、培养团队合作能力、沟通能力、创新能力以及组织能力。

三、课题要求: 1.基本要求

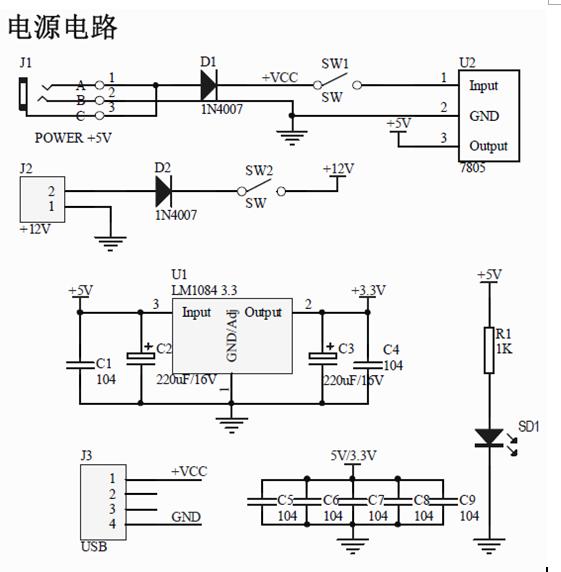

(1)输入电源:12V;

(2)具有前进、左转、右转、自动停车的功能;

(3)能根据提供的8字循迹路线进行寻迹。

2.发挥部分

(1)按键启动; (2)转向提示; (3)鸣号提示; 摘要:本循迹小车是AT89C51单片机为控制核心,加以直流电机,电源电路以及其他电路构成。系统AT89C51通过I/O控制小车前进及转向。寻迹由光敏电阻组成光敏探测器完成。

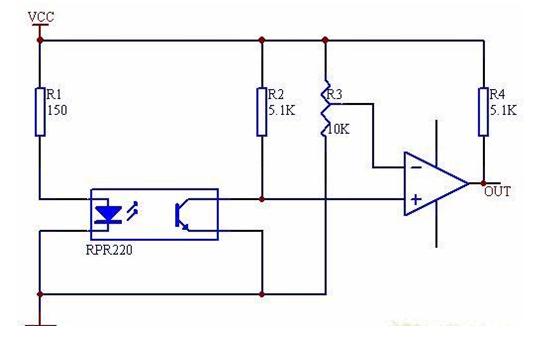

四、小车循迹原理: 本智能循迹小车以AT89C51单片机为核心控制系统,用光敏电阻组成光敏探测器。光敏电阻的阻值可以跟随周围环境光线的变化而变化。当光线照射到白线上面时,光线反射强烈,光线照射到黑线上面时,光线反射较弱。因此光敏在白线和黑线上面上方时,阻值会发生明显的变化。将阻值的变化值经过比较器就可以输出高低电平。经单片机处理后,输出控制信号给电机驱动电路,来控制电机的驱动。所以整个过程不需要人来控制,当不同的光敏电阻检测到黑线时,电机会有不同的转动方向。从而实现了简单的智能控制。

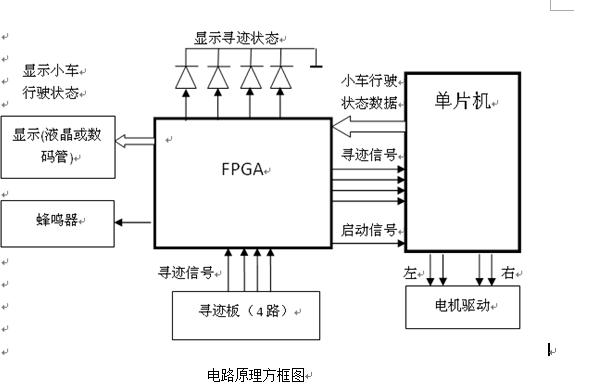

五、硬件设计1、总体设计

电路原理方框图

2、单片机控制系统模块设计

我们采用AT89C52片机最小系统电路为整个系统的控制系统,它负责控制小车的运动状态。

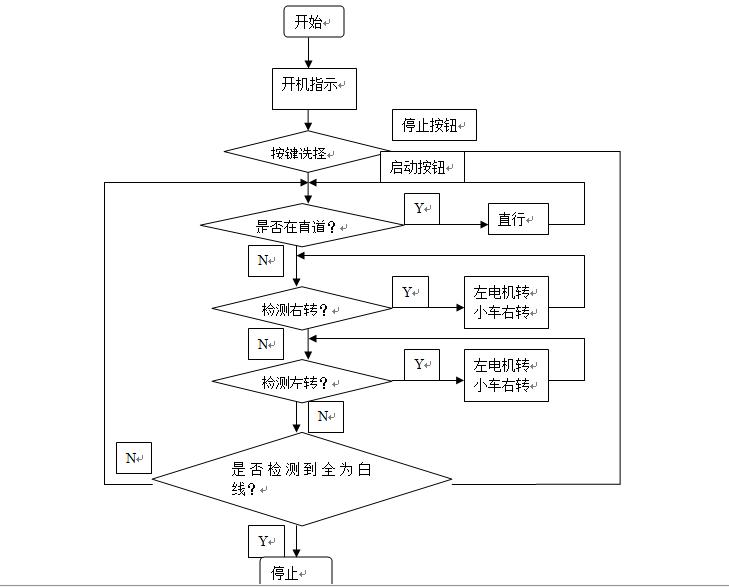

(1)启动小车 小车在接收到FPGA送过来的启动指令后,读取寻迹信号,根据寻迹信号确定小车的运行状态,将小车的运行状态送至FPGA,同时根据相应算法,驱动小车的左右电机前进。 (2)正常前进 当寻迹板中间两个传感器检测到黑线(任意一个检测到黑线或两个同时检测到黑线),小车都正常前进。 (3) 左拐弯 当最左端的传感器检测到黑线,右端3个传感器检测到白色时,小车应左拐弯。 (4) 右拐弯 当最右端的传感器检测到黑线,左端3个传感器检测到白色时,小车应右拐弯。 (5)后退 当4个传感器都检测到白色,小车后退。 (6) 停车 当4个传感器同时连续多次检测到黑线(如连续3次),小车停车。小车停车后,发出一个停车标志信号送给FPGA。 3、寻迹模块的设计

寻迹板送过来的4路检测信号送到FPGA板,FPGA将此4路信号送出至4个LED灯显示状态(检测至黑线亮,否则灭);同时将此4路信号送到单片机。

4、显示模块的设计

我们采用的是数码管显示。 (1) 小车启动 小车启动时,显示“1”。 (2)小车左拐 小车左拐时,显示“2”。 (3) 小车右拐 小车右拐时,显示“3”。 (4)小车前进 小车前进时,显示“4”。 (5) 小车后退 小车后退时,显示“5”。 (6) 停车 小车停车时,显示“6”。

5、提示音模块的设计

(1) 小车启动 小车启动前发出3声“嘟、嘟、嘟”的声音,提示音结束后,FPGA发出一个启动信号给单片机,从而启动小车。 (2) 停车 小车停车时,FPGA播放一首音乐,音乐播放结束即表示小车完成了任务。 6、FPGA模块的设计 (1) 寻迹信号处理 寻迹板过来的信号一方面送到LED灯显示寻迹状态,另一方面要将此信号送到单片机去处理。 (2) 小车状态显示 将小车的运行状态用数码管显示出来。 (3) 提示音 小车启动前,发出3声提示音。小车停车后播放一首音乐。 (4) 小车启动 小车在发出3声提示音后,FPGA发出一个开始指令给单片机,从而启动小车前进。 (5) 小车停车 小车停车后,FPGA接收到单片机的停车指令,开始播放音乐,直到一首音乐播放完毕。 7、电机驱动模块设计 我们选用电机驱动芯片L298N。L298N为单块集成电路,高电压,高电流,四通道驱动,可直接是对电机进行控制,无需隔离电路,通过单片机的I/O输入改变控制端的电平,即可以对电机进行正反转,停止的操作,非常方便,亦能满足直流减速电机的大电流要求。调试时在依照上表,用程序输入对应的码值,能够实现对应的动作。下表是其使能、输入引脚和输出引脚的逻辑关系。

六、软件设计 智能小车的控制使用ATMEL公司的AT89C51单片机。程序设计上,通过对检测信号的采集、分析数据,判断出小车的运行状态,进而控制小车沿黑线行驶。

主程序流程图

七、程序设计:1、单片机C语言程序设计: #include<reg51.h> #define uchar unsigned char #define uint unsigned int unsigned char w0=0; unsigned char w1=0; unsigned char t=0; sbit RT1=P1^0; sbit RT2=P1^1; sbit LT1=P1^2; sbit LT2=P1^3; sbit IN1=P0^0; sbit IN2=P0^1; sbit IN3=P0^2; sbit IN4=P0^3; sbit ENA=P0^4; sbit ENB=P0^5; void delay(int z) { while(z--); } void init() { TMOD=0x01; TH0=(65536-100)/256; TL0=(65536-100)%256; EA=1; ET0=1; TR0=1; } void time0()interrupt 1 { if(t<w0) ENA=1; else ENA=0; if(t<w1) ENB=1; else ENB=0; t++; if(t>=100) {t=0;} } void qianjin() { w0=30; w1=30; } void turn_left1() {w0=0; w1=50; } void turn_left2() {w0=0; w1=60; } void turn_right1() {w0=50; w1=0; } void turn_right2() {w0=60; w1=0; } void xunji() { uchar flag; if((RT1==1)&&(RT2==1)&&(LT1==1)&&(LT2==1)) {flag=0;}//直行 else if((RT1==0)&&(RT2==1)&&(LT1==1)&&(LT2==1)) {flag=1;}//右转1 else if((RT1==0)&&(RT2==0)&&(LT1==1)&&(LT2==1)) {flag=2;}//2 else if((RT1==1)&&(RT2==1)&&(LT1==0)&&(LT2==1)) {flag=3;}//左转1 else if((RT1==1)&&(RT2==1)&&(LT1==0)&&(LT2==0)) {flag=4;}//2 switch(flag) { case0:qianjin(); break; case1:turn_righ1t(); break; case2:turn_right2(); break; case3:turn_left1(); break; case4:turn_left2(); break; } } void main() {init(); w0=30; w1=30; while(1) { IN1=1; IN2=0; IN3=1; IN4=0; ENA=1; ENB=1; while(1) {xunji(); } } } 2、循迹程序设计: #include<reg52.h> #define uchar unsigned char #define uint unsigned int uint tt=0,flag=0,flag1=0,flag2=0,num=0; sbit in1=P2^0; sbit in2=P2^1; sbit in3=P2^2; sbit in4=P2^3; sbit a=P0^0; sbit b=P0^1; sbit c=P0^2; sbit d=P0^3; sbit ENA=P2^4; sbit ENB=P2^5; sbit control=P1^0; sbit FPGA1=P1^1; sbit FPGA2=P1^2; sbit FPGA3=P1^3; sbit FPGA4=P1^4; sbit buzzer=P1^5; void init_time(); void delay(unsigned int z); void Turn_left() { in1=0; in2=0; in3=1; in4=0; } void Turn_right() { in1=1; in2=0; in3=0; in4=0; } void Go() { in1=1; in2=0; in3=1; in4=0; } void Back() { in1=0; in2=1; in3=0; in4=1; } void Stop() { in1=1; in2=1; in3=1; in4=1; } void Go_left_right() { in1=1; in2=0; in3=0; in4=1; } /*void Go_right() { in1=0; in2=1; in3=0; in4=0; }*/ void FPGA_display() { FPGA1=a; FPGA2=b; FPGA3=c; FPGA4=d; } void FPGA_display1() { FPGA1=a&0; FPGA2=b|1; FPGA3=c|1; FPGA4=d&0; } void main() { uint i=10; init_time(); delay(2); control=0; buzzer=1; //P0=0xff; //P1=0xff; //delay(2000); //delay(2000); //Go(); //delay(100); while(!control) { delay(2); FPGA_display1(); //delay(200); //delay(200); } if(control==1) { delay(300); Go(); delay(100); Go(); delay(100); while(2) { if((a==0&&b==0&&c==1&&d==1)||(a==0&&b==0&&c==0&&d==1)||(a==0&&b==0&&c==1&&d==0)) Turn_right();FPGA_display(); delay(30); if((a==1&&b==1&&c==0&&d==0)||(a==1&&b==0&&c==0&&d==0)||(a==0&&b==1&&c==0&&d==0)) Turn_left();FPGA_display(); delay(30); if(a==0&&b==1&&c==1&&d==0) Go();FPGA_display(); delay(9); if(a==0&&b==0&&c==0&&d==0) { Back();FPGA_display(); delay(10); Back(); delay(10); Back(); flag1++; flag2++; if(flag2==13) flag2=0; if(flag1==8) flag1=0; } if(flag1==7) { flag1=0; Go(); delay(60); Go(); delay(60); Go(); delay(60); Go(); delay(60); } delay(5); if(a==1&&b==1&&c==1&&d==1) { flag++; if(flag==12) flag=4; } if(flag==1||flag==2||flag==3) { Stop(); //Turn_right(); delay(100); Stop(); delay(100); Back(); delay(100); Back(); delay(100); Back(); delay(300); Back(); delay(300); Turn_right(); delay(500); Turn_right(); delay(500); Turn_right(); delay(500); //Back(); //delay(200); //Turn_left(); Turn_right(); delay(500); //Turn_left(); Turn_right(); delay(400); //Turn_left(); Turn_right(); delay(300); //Turn_left(); Turn_right(); delay(200); flag=4; Go(); delay(10); } //if(flag>=2) //{ // Go(); // delay(50); //} //Go(); //Back(); } } } void delay(unsigned int z) { unsigned int i,j; for(i=z;i>0;i--) for(j=110;j>0;j--); } void init_time() { TMOD=0x01; TH0=(65536-25000)/256; TL0=(65536-25000)%256; EA=1; TR0=1; ET0=1; } void time_0(void) interrupt 1 { TH0=(65536-20000)/256; TL0=(65536-20000)%256; tt++; num++; if(num==500) { num=0; buzzer=0; } //delay(1); if(tt>=9) tt=0; if(tt<=4) { ENA=1; ENB=1; } else { ENA=0; ENB=0; } } |