一直感觉这是个很简单的问题,直到突然自己连BCD都不太清楚的时候,才发现这没有看起来那么简单,这里介绍里任意位二进制转为BCD的verilog代码,这个转换方法也可以用在C上面,此为原创,转载请注明,谢谢。

基础知识:

BCD:BCD码又称为8421码,

意义:之所以有时候需要将binary转换为BCD,一般是用在本科的实验中,为了将binary显示在数码管中,当然还有很多应用,只是目前我还没有用到。

转换算法:左移加3法

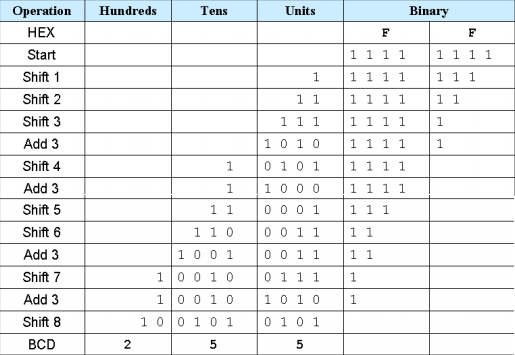

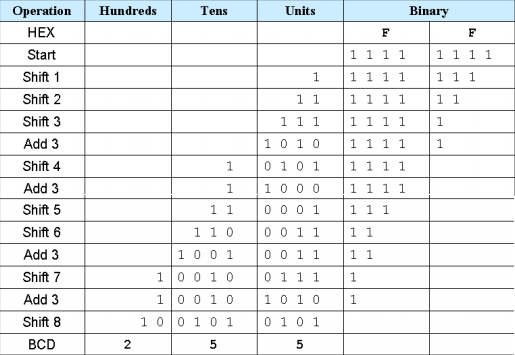

移位加3法的具体原理,在网上感觉也没有人能够说的清楚,以后找到书籍再说吧。下面解释下左移加三算法。这里以8bit二进制数FF做例子。

该算法的操作为上图。下面对上图的操作进行详细的解释:

由于8bit的二进制最大为FF,转换为十进制为255。所以需要使用三个BCD码来表示所有的8bit二进制数。上图的hundreds表示百位的BCD,tens表示十位的BCD,Units表示个位的BCD。算法的操作为一直将binary数据左移,移出的数据按顺序存在hundreds,tens,Units。例如上面的shift1,shift2,shift3操作后,Units变为了0111,至于为何在shift3后进行add3操作,是因为在算法中每一次左移,都要对hundreds,tens和Units进行判断,如果hundreds,tens和Units里面的值大于或等于5,就将hundreds,tens和Units自加3.所以shift3后,Units里面为0111,表示为7,此时不能左移,而是对Units加三操作,所以Units的值从0111变为了1010.值得注意的是,只要hundreds,tens和Units中任意一个的值大于或等于5(0101),就要先进行一次自加三的操作,然后才能继续左移,后面的操作同上。

注意2:n位的binary就需要进行n次左移

注意3:最后一次左移不需要进行add3操作

注意4

: 亲自推导16位的,和24位的binary转换,结果正确,所以该算法适用于任意位binary

to BCD,当然这种论断没有足够的理论依据。

verilog代码:

说明:对于8bit及以下的binary,可以使用case语句实现移位加三算法。由于这里说明的是任意位的二进制数,转为BCD,所以我的代码中设计了一个状态机,来控制移位,加三和结束操作。由于代码编写时间仓促,其中或许有些bug。

//name:

二进制转BCD

//data: 2014-04-17 at kb129

//info: as 2**8=255 change to BCD then this need

3 times of “8421”

module b_to_bcd(

clk,

rst_n,

binary,

state_en,

BCD

);

parameter

b_length

= 8;

parameter

bcd_len

= 12;

parameter

idle

= 5'b00001;

parameter

shift

= 5'b00010;

parameter

wait_judge = 5'b00100;

parameter

judge

= 5'b01000;

parameter

add_3

= 5'b10000;

input

clk;

input

rst_n;

input

[b_length-1:0]

binary;

input state_en;

output reg [bcd_len-1:0]

BCD;

reg

[b_length-1:0]

reg_binary;

reg [3:0]

bcd_b, bcd_t,

bcd_h;

reg [3:0]

shift_time;

reg [5:0]

c_state,

n_state;

reg add3_en;

reg change_done;

//this is a three section kind of state code

style

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

c_state <= idle;

else

c_state <= n_state;

end

//the second section

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

c_state <= idle;

else

case(n_state)

idle:begin

if((binary!=0)&&(state_en==1'b1)&&(change_done==0'b0))

n_state <= shift;

else

n_state <= idle;

end

shift: n_state <= wait_judge;

wait_judge:

begin